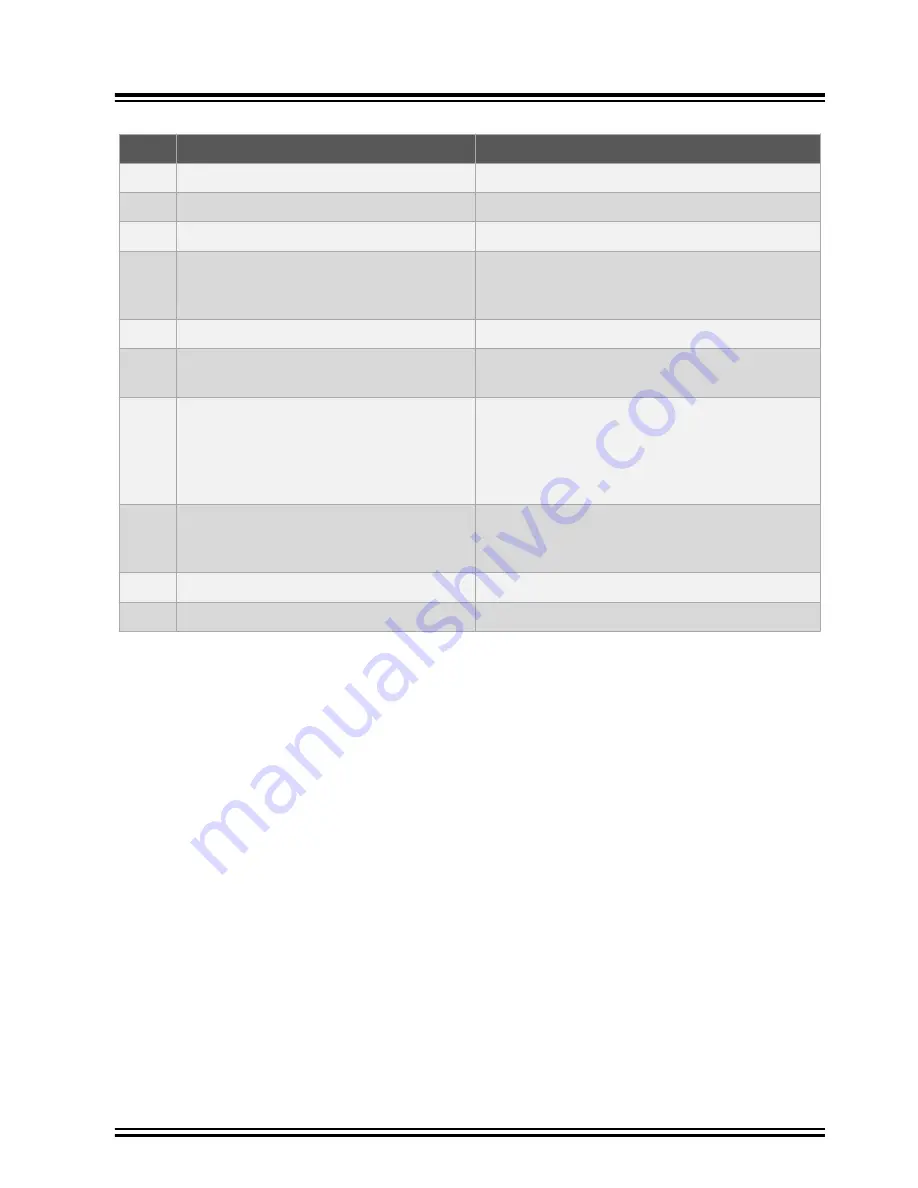

Table 3-17. JTAG/ICE Connector J2 Pin Assignment

Pin No Mnemonic

Signal Description

1

VTref. 3.3V power

This is the target reference voltage (main 3.3V).

2

TMS TEST MODE SELECT

JTAG mode set input into target CPU

3

GND

Common ground

4

TCK TEST CLOCK - Output timing signal,

for synchronizing test logic and control

register access

JTAG clock signal into target CPU

5

GND

Common ground

6

TDO JTAG TEST DATA OUTPUT - Serial

data input from the target

JTAG data output from target CPU

7

RTCK - Input return test clock signal from

the target

Some targets with a slow system clock must

synchronize the JTAG inputs to internal clocks. In

the present case, such synchronization is

unneeded and TCK is merely looped back into

RTCK.

8

TDI TEST DATA INPUT - Serial data output

line, sampled on the rising edge of the TCK

signal

JTAG data input into target CPU

9

GND

Common ground

10

nRST RESET

Active-low reset signal. Target CPU reset signal.

3.4.2

Embedded Debugger (JLINK-OB) Interface

The SAMA5D2-PTC-EK includes a built-in SEGGER J-Link-On-Board device. The functionality is

implemented with an ATSAM3U4C microcontroller in an LFBGA100 package. The ATSAM3U4C provides

the functions of JTAG and a bridge USB/Serial debug port (CDC). One two-colored LED (D6) mounted

near the SAM3 chip (U20) shows the status of the J-Link-On-Board device.

J-Link-OB-ATSAM3U4C was designed in order to provide an efficient, low-cost, on-board alternative to

the standard J-Link.

The USB JLINK-OB port is used as a secondary power source and as a communication link for the

board, and derives power from the PC over the USB cable. This port is limited in most cases to 500 mA.

A single PC USB port is sufficient to power the board.

SAMA5D2-PTC-EK

Board Components

©

2017 Microchip Technology Inc.

DS50002709A-page 37