the slave address. Next follows a number of data

bytes. The slave returns an acknowledge bit after

each received byte. Data is transferred with the most

significant bit (MSB) first.

Data transfer from a slave transmitter to a master

receiver.

The first byte (the slave address) is trans-

mitted by the master. The slave then returns an

acknowledge bit. Next follows a number of data

bytes transmitted by the slave to the master. The

master returns an acknowledge bit after all received

bytes other than the last byte. At the end of the last

received byte, a not acknowledge is returned.

The master device generates all the serial clock puls-

es and the START and STOP conditions. A transfer is

ended with a STOP condition or with a repeated

START condition. Since a repeated START condition

is also the beginning of the next serial transfer, the

bus will not be released. Data is transferred with the

most significant bit (MSB) first.

DS3232

Extremely Accurate I

2

C RTC with

Integrated Crystal and SRAM

____________________________________________________________________

17

...

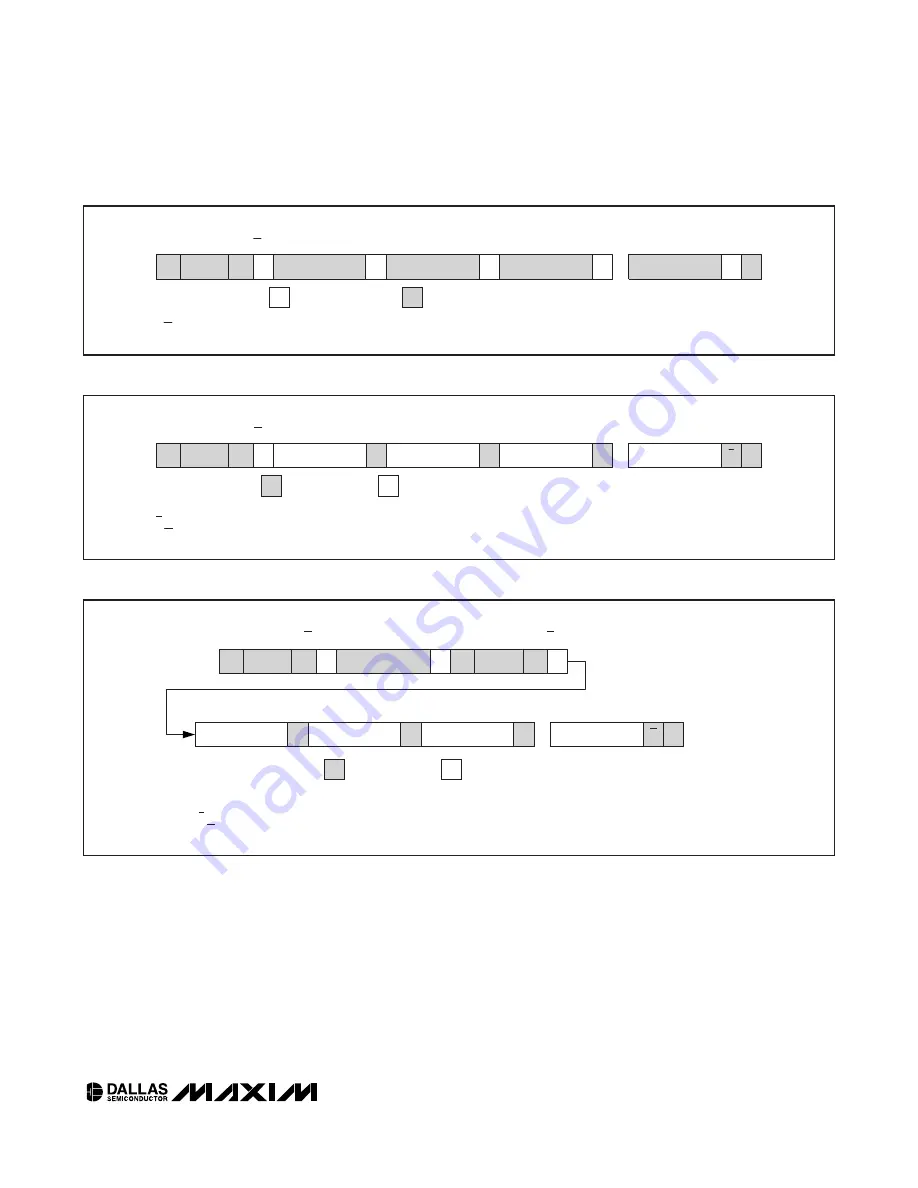

A

XXXXXXXX

A

1101000

S

0

XXXXXXXX

A

XXXXXXXX

A

XXXXXXXX

A

P

<R/W> <WORD ADDRESS (n)> <DATA (n)> <DATA (n + 1)> <DATA (n + X)

S - START

A - ACKNOWLEDGE (ACK)

P - STOP

R/W - READ/WRITE OR DIRECTION BIT ADDRESS

DATA TRANSFERRED

(X + 1 BYTES + ACKNOWLEDGE)

MASTER TO SLAVE

SLAVE TO MASTER

<SLAVE

ADDRESS>

Figure 3. Data Write—Slave Receiver Mode

...

A

XXXXXXXX

A

1101000

S

1

XXXXXXXX

A

XXXXXXXX

A

XXXXXXXX

A

P

S - START

A - ACKNOWLEDGE (ACK)

P - STOP

A - NOT ACKNOWLEDGE (NACK)

R/W - READ/WRITE OR DIRECTION BIT ADDRESS

DATA TRANSFERRED

(X + 1 BYTES + ACKNOWLEDGE)

NOTE: LAST DATA BYTE IS FOLLOWED BY A NACK.

MASTER TO SLAVE

SLAVE TO MASTER

<R/W> <DATA (n)> <DATA (n + 1)> <DATA (n + 2)> <DATA (n + X)>

<SLAVE

ADDRESS>

Figure 4. Data Read—Slave Transmitter Mode

S - START

Sr - REPEATED START

A - ACKNOWLEDGE (ACK)

P - STOP

A - NOT ACKNOWLEDGE (NACK)

R/W - READ/WRITE OR DIRECTION BIT ADDRESS

<R/W>

<WORD ADDRESS (n)>

<SLAVE ADDRESS (n)>

<SLAVE

ADDRESS>

<R/W>

A

XXXXXXXX

A

1101000

1101000

S

Sr

0

A

1

DATA TRANSFERRED

(X + 1 BYTES + ACKNOWLEDGE)

NOTE: LAST DATA BYTE IS FOLLOWED BY A NACK.

MASTER TO SLAVE

SLAVE TO MASTER

A

XXXXXXXX

XXXXXXXX

A

XXXXXXXX

A

XXXXXXXX

A

P

<DATA (n)> <DATA (n + 1)> <DATA (n + 2)> <DATA (n + X)>

...

Figure 5. Data Write/Read (Write Pointer, Then Read)—Slave Receive and Transmit