43

44

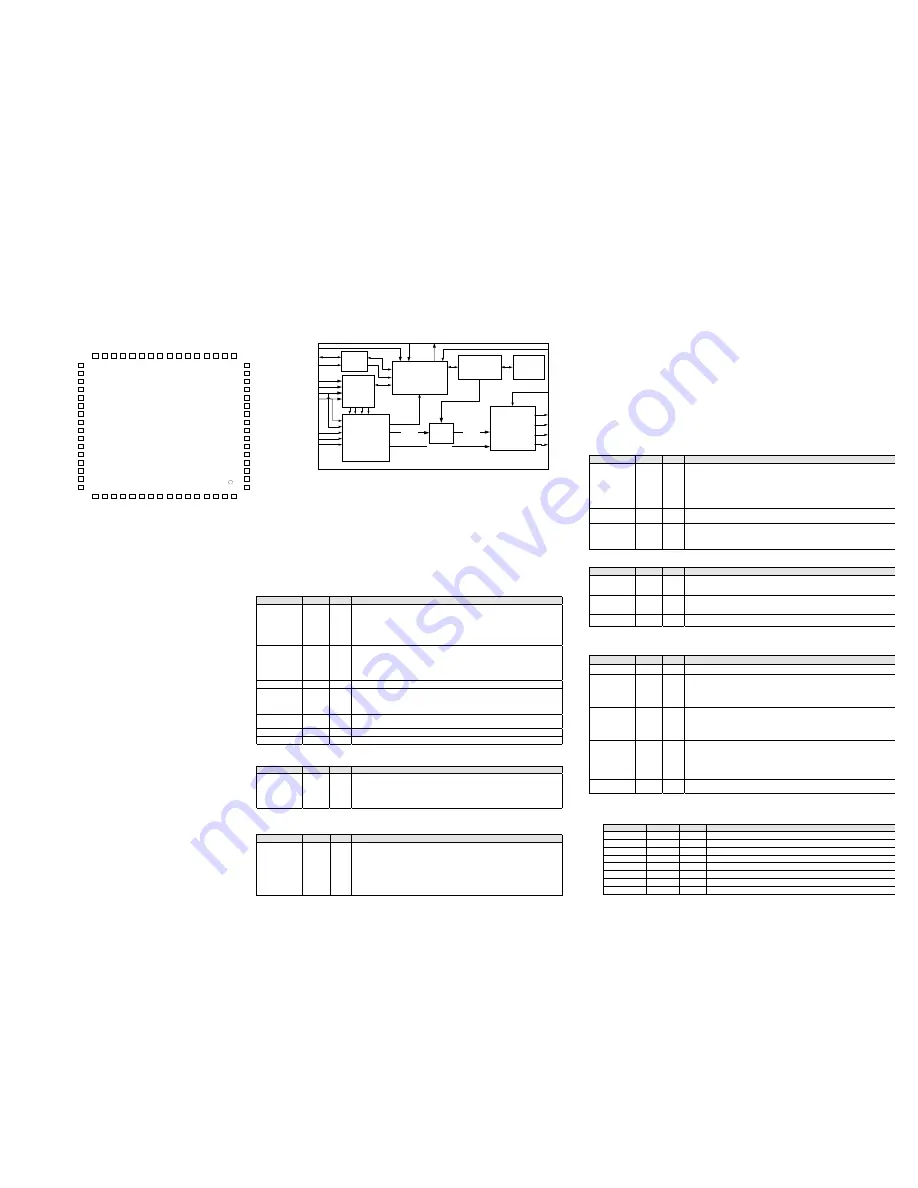

QT03:SiI 170B

V C C

D E

V R E F

H SY N C

V S Y N C

C TL3

N C

N C

H T PL G

P D #

M SE N

V C C

IS EL/R S T#

S D A S

S C L S

G N D

PGN

D1

PVC

C1

EXT

_SWI

N

G

AGN

D

TXC

-

TXC

+

AVC

C

TX0

-

TX0

+

AGN

D

TX1

-

TX1

+

AVC

C

TX2

-

TX2

+

V C C

RE S E RV E D

G N D

D 23

D 22

D 21

D 20

D 19

D 18

D 17

D 16

D 15

D 14

D 13

D 12

P G N D 2

PVC

C2

D1

1

D1

0

D9

D8

D7

D6

IDCK

-

IDCK+

D5

D4

D3

D2

D1

D0

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

Si

I 170 B

64- P in LQ FP

(Top Vi e w )

AGND

HDCP

Encryption

Engine

HDCP

Keys

EEPROM

Registers

----------------

Configuration

Logic Block

Panel Li nk

TM DS

TM

Digital

Core

XOR

Mask

encrypted

data

Data

Capture

Logic

Block

clear data

control signals

I

2

C

Slave

DE

Gen

CTL3

DE

D[23:0]

SDAS

SCLS

HSYNC

VSYNC

IDCK+

IDCK-

EXT_SWING

TXC±

TX0±

TX1±

TX2±

HTPLG

PD#

ISEL/RST#

MS

E

N

Functional Block Diagram

Input Pins

Pin Name

Pin #

Type Description

D23-D12

See Pin

Diagram

In

Upper 12 bits of 24-bit pixel bus. Mode controlled by configuration register bit:

When BSEL = HIGH, this bus inputs the top half of the 24-bit pixel bus.

When BSEL = LOW, these bits are not used to input pixel data. In this mode, the

state of D[23:16] is input to the I

2

C register CFG. This allows an extra 8-bits of user

configuration data to be read by the graphics controller through the I

2

C interface

(see I

2

C register definition).

D11–D0 See

Pin

Diagram

In

Bottom half of 24-bit pixel bus / 12-bit pixel bus input. Mode controlled by

configuration register bit:

When BSEL = HIGH, this bus inputs the bottom half of the 24-bit pixel bus.

When BSEL = LOW, this bus inputs ½ a pixel (12-bits) at every latch edge (both

falling and/or rising) of the clock.

IDCK+

57

In

Input Data Clock +. This clock is used for all input modes.

IDCK-

56

In

Input Data Clock –. This clock is only used in 12-bit mode when dual edge clocking

is turned off (DSEL = LOW). It is used to provide the ODD latching edges for multi-

phased clocking. If (BSEL = HIGH) or (DSEL = HIGH) this pin is unused and should

be tied to GND.

DE

2

In

Data enable. This signal is high when input pixel data is valid to the transmitter and

low otherwise.

HSYNC

4

In

Horizontal Sync input control signal.

VSYNC

5

In

Vertical Sync input control signal.

Input Voltage Reference Pin

Pin Name

Pin #

Type Description

VREF

3

Analog

In

Must be tied to 3.3V.

Power Management Pin

Pin Name

Pin #

Type Description

PD#

10

In

Power Down (active LOW). A HIGH level (3.3V) indicates normal operation and a

LOW level (GND) indicates power down mode. During power down mode, the I

2

C

pins are active, but digital input, output buffers and the PanelLink Digital core are

powered down. This pin should be tied LOW to ensure the chip is powered off when

RESET is asserted.

When PD# is asserted, the differential output pins for TMDS are tri-stated until the

PD# register bit is asserted through I

2

C.

Differential Signal Data Pins

Pin Name

Pin #

Type Description

TX0+

TX0-

TX1+

TX1-

TX2+

TX2-

25

24

28

27

31

30

Analog

Analog

Analog

Analog

Analog

Analog

TMDS Low Voltage Differential Signal output data pairs.

These pins are tri-stated when PD# is asserted.

TXC+

TXC-

22

21

Analog

Analog

TMDS Low Voltage Differential Signal output clock pairs.

These pins are tri-stated when PD# is asserted.

EXT_SWING

19

Analog Voltage Swing Adjust. A resistor should tie this pin to AVCC. This resistor

determines the amplitude of the voltage swing. A 510 ohm resistor is recommended

for remote display applications. For notebook computers, 680 ohm is

recommended.

Configuration/Programming Pins

Pin Name

Pin #

Type Description

MSEN

11

Out

Monitor Sense. This pin is an open collector output. The output is programmable

through the I

2

C interface (see I

2

C register definitions). An external 5K pull-up

resistor is required on this pin.

RESERVED

34

In

This pin is reserved for Silicon Image use only and should be tied LOW for normal

operation.

NC

7,8

NC

These pins are not electrically connected inside the package.

Control Pins

These control pins allow configuration of the transmitter through the slave I

2

C port, which is required by HDCP.

Pin Name

Pin #

Type Description

ISEL/RST# 13

In

I

2

C Interface Select. If HIGH, then the I

2

C interface is active.

SCLS 1

5

In

DDC I

2

C Clock. This pin is a slave I

2

C clock line which interfaces to the DDC bus for

communicating with a host side master. HDCP KSV, A

n,

and R

i

values are

exchanged over this DDC bus during authentication. The clock may be run up to

400kHz. This pin is not 5V-tolerant; it should be connected through a level shifter to

the DDC clock line SCL. This is an open-collector pin.

SDAS 1

4

In/Out DDC I

2

C Data. This pin is a slave I

2

C data line for communicating with a host side

master. HDCP KSV, A

n,

and R

i

values are exchanged over this DDC bus during

authentication. Data may be clocked in at up to 400kHz. This pin is not 5V-tolerant;

it should be connected through a level shifter to the DDC clock line SDA. This is an

open-collector bi-directional pin, and is not made high-impedance when PD#=LOW.

CTL3

6

In

External CTL3. This pin is used to bring in the CTL3 signal for HDCP when the

HDCP encryption is performed before the video enters the SiI 170. To enable this

input, the CTL3 bit must be programmed in Reg[0x08]. If the CTL3 bit is cleared,

then this input pin is ignored and may be left unconnected. This pin is a regular high

swing (3.3V) input, containing a weak pull-down resistor so that if left unconnected it

will default to LOW.

HTPLG

9

In

Monitor Charge Input. This pin is used to connect to the DVI Hot Plug pin to detect

the presence of an attached monitor.

Power and Ground Pins

Pin Name

Pin #

Type Description

VCC

1,12,33

Power

Digital VCC. Connect to 3.3V supply.

GND 16,35,64 Ground

Digital

GND.

AVCC

23,29

Power

Analog VCC. Connect to 3.3V supply.

AGND 20,26,32 Ground

Analog

GND.

PVCC1

18

Power

Primary PLL Analog VCC. Connect to regulated 3.3V supply.

PVCC2

49

Power

Filter PLL Analog VCC. Connect to regulated 3.3V supply.

PGND1

17

Ground

PLL Analog GND.

PGND2

48

Ground

PLL Analog GND.