2-25

R

F

H / O

P

INN /

RF

G /

OP

IN

P

/

RF

IN

/

OPOUT

/

RF

IP

AG

N

D

1

8

AVDD1

8

_

1

ADACVDD2

ADACVDD1

ALF / CENT

E

R / GPIO

ALS / GPIO

AL / G

P

IO

1

AVCM

AR

/ G

P

IO

0

ARS / GPIO

AR

F / LFE / GPIO

A

A

DV

DD

AKIN

1

/ GPIO21 / Aud

io_m

u

te

ADVCM / GPIO2

0

/

AKIN

2

/ GPIO19 / Aud

io_m

u

te

A

D

A

C

VSS1

A

D

A

C

VSS2

APL

LCAP

APL

L

V

DD

AA

D

VS

S

R

B

G

DA

CVDDA

DA

CVDDB

CV

BS

DA

CVS

SC

FS

12

8

12

7

12

6

12

5

12

4

12

3

12

2

12

1

12

0

11

9

11

8

11

7

11

6

11

5

11

4

11

3

11

2

11

1

11

0

10

9

10

8

10

7

10

6

10

5

10

4

10

3

10

2

10

1

10

0

99

98

97

RFA

1

96

VREF

RFB

2

95

DACVDDC

RFC

3

94

GPIO13

RFD

4

93

SPDIF / GPIO12

RFE

5

92

RFF

6

91

GPIO11

GPIO10

7

90

AVDD18_2

DVDD18

AVDD33_1

8

89

GPIO9

XTALI

9

88

GPIO8

XTALO

10

87

GPIO7 / CKE

AGND33

11

86

RA3

V20

12

85

RA2

V14

13

84

DVDD33

REXT

14

83

RA1

MDI1

15

82

RA0

MDI2

16

81

RA10

LDO1

17

80

BA1

LDO2

18

79

DVSS18

AVDD33_2

19

78

BA0

DMO

20

77

RAS#

FMO

21

76

CAS#

TRAY_OPEN

22

75

RWE#

TRAY_CLOSE

23

74

RA4

TRO

24

73

RA5

FOO

25

72

RA6

26

71

RA7

USB_DP

27

70

RA8

USB_DM

28

69

RA9

VDD33_USB

29

68

DVDD33

VSS33_USB

30

67

RA11

PAD_VRT

31

66

RCLK

VDD18_USB

32

65

DQM1

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

SF_

C

S

_

SF_

D

O

SF_

D

I

SF_

C

K

UP1_6 / SC

L

UP1_7 / SD

A

IC

E

PR

S

T

#

IR

RD

0

RD

1

RD

2

RD

3

RD

4

DVDD33

RD

5

RD

6

RD

7

DVDD18

DQ

M

0

RD15

RD14

RD13

RD12

DVSS33

RD11

RD10

RD

9

RD

8

MT1389L

FG / GPIO2

GPIO3

/

I

N

T

#

GPIO4

GPIO6

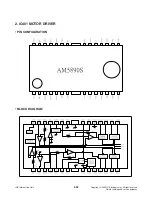

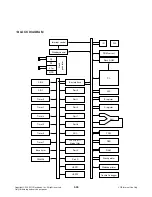

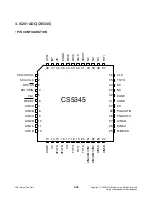

1. IC501 MPEG(MT1389L)

• PIN CONFIGURATION

INTERNAL BLOCK DIAGRAM OF ICs

Copyright © 2009 LG Electronics. Inc. All right reserved.

Only for training and service purposes

LGE Internal Use Only