2-39

VLS

0.1

µ

F

+1.8V

to +5V

DGND

VLC

0.1

µ

F

+1.8V

to +5V

SCL/CCLK

SDA/CDOUT

AD1/CDIN

RESET

2 k

See Note 1

AGND

AD0/CS

Note 1: Resistors are required

for IC control port operation

Micro-

Controller

0.1

µ

F

VA

* Capacitors must be C0G or equivalent

Digital Audio

Capture

LRCK

SDOUT

MCLK

SCLK

PGAOUTA

PGAOUTB

2.2nF

AFILTA

AFILTB

OVFL

2.2nF

3.3

µ

F

3.3

µ

F

47

µ

F

0.1

µ

F

VQ

FILT+

10

µ

F

AGND

*

*

2 k

INT

47

µ

F

AIN1A

Left Analog Input 1

10

µ

F

10

µ

F

1800 pF

1800 pF

100 k

100 k

100

100

AIN1B

Right Analog Input 1

AIN2A

Left Analog Input 2

10

µ

F

10

µ

F

1800 pF

1800 pF

100 k

100 k

100

100

AIN2B

Right Analog Input 2

AIN3A

Left Analog Input 3

10

µ

F

10

µ

F

1800 pF

1800 pF

100 k

100 k

100

100

AIN3B

Right Analog Input 3

AIN4A/MICIN1

Left Analog Input 4

10

µ

F

10

µ

F

1800 pF

1800 pF

100 k

100 k

100

100

AIN4B/MICIN2

Right Analog Input 4

AIN5A

Left Analog Input 5

10

µ

F

10

µ

F

1800 pF

1800 pF

100 k

100 k

100

100

AIN5B

Right Analog Input 5

AINA

Left Analog Input ;

10

µ

F

10

µ

F

1800 pF

1800 pF

100 k

100 k

100

100

AIN6B

Right Analog Input 6

MICBIAS

AGND

0.1

µ

F

*

*

*

*

*

*

*

*

*

*

*

*

NC

NC

NC

NC

NC

TSTI

TSTO

TSTO

TSTO

10

µ

F

+3.3V to +5V

0.1

µ

F

10

µ

F

0.1

µ

F

VA

VD

+3.3V to +5V

R

L

See Note 2

Note 2 The value of R

L

is

dictated by the microphone

carteridge.

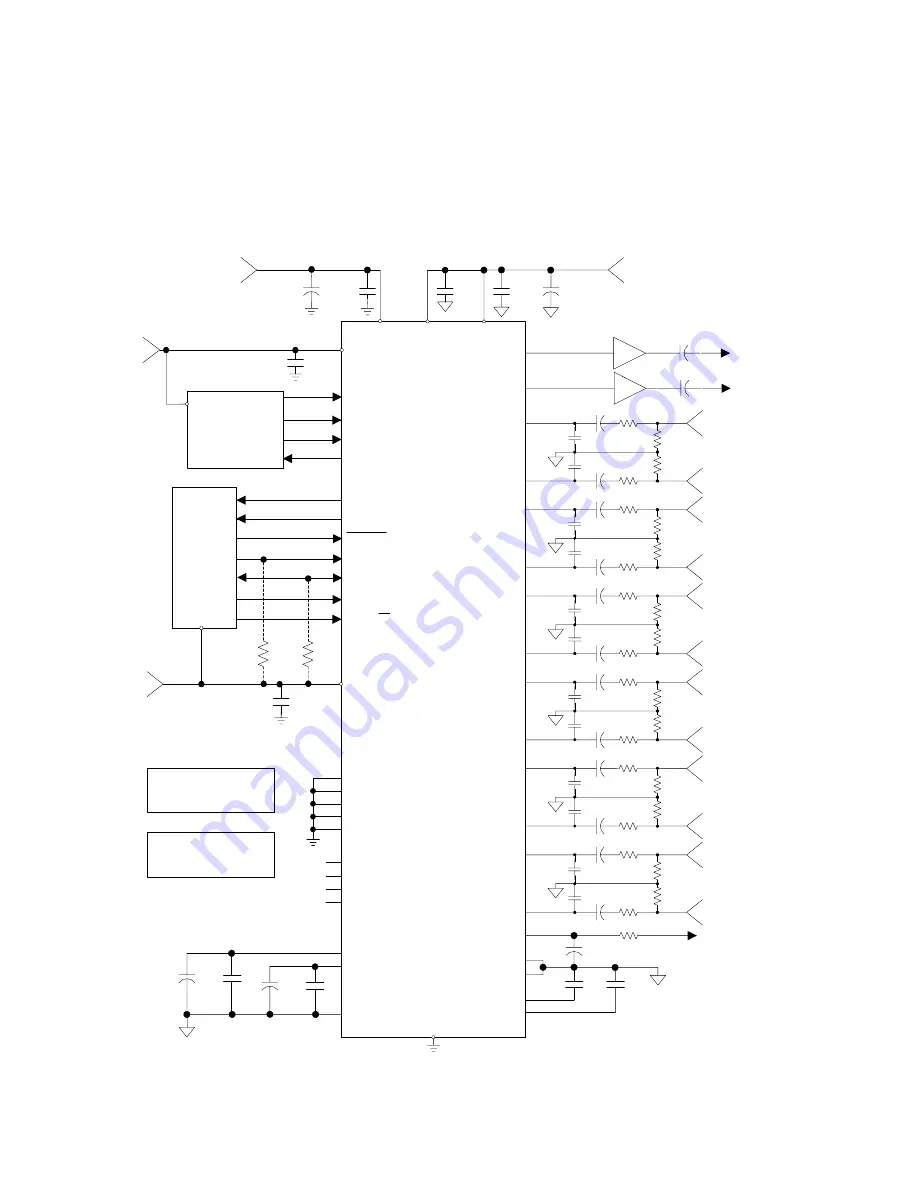

4. IC201 ADC(CS5345)

• BLOCK DIAGRAM

Copyright © 2009 LG Electronics. Inc. All right reserved.

Only for training and service purposes

LGE Internal Use Only