30

ECP5 PCI Express Board User’s Guide

5

5

4

4

3

3

2

2

1

1

D

D

C

C

B

B

A

A

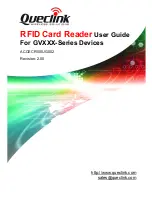

System Clock Generation

System 54MHz Clock

CLK54-EXTa => AD32 LRC_GPLL0T_IN

CLK54-EXTb => A17 PCLKT0_1

CLK54a => Card #1

CLK54b => Card #2

External Clock Source

Clock Destinations

All clock routing

should be 50 Ohm

50 Ohm Clock Route

Place termination close to X1

50 Ohm Clock Route

Place termination

close to U4

REFSEL1

CLK54

CLKEXT

CLKEXT

CLK54

PLL_BYPASS

2_5V

3_3V

2_5V

3_3V

2_5V

CLK_TDO

[Pg9]

CLK_TMS

[Pg9]

CLK_TCK

[Pg9]

CLK54a

[Pg13]

CLK54b

[Pg14]

CLK54-EXTa

[Pg20]

CLK54-EXTb

[Pg19]

CLK_TDI

[Pg9]

CLK_REFSEL1

[Pg10]

CLK_PLL_BYPASS

[Pg10]

Date:

Size

Schematic Rev

of

Sheet

Title

Lattice Semiconductor Applications

Email: [email protected]

Board Rev

Project

Nov, 2012

B

B

28

12

Clock Generation

B

Date:

Size

Schematic Rev

of

Sheet

Title

Lattice Semiconductor Applications

Email: [email protected]

Board Rev

Project

Nov, 2012

B

B

28

12

Clock Generation

B

Date:

Size

Schematic Rev

of

Sheet

Title

Lattice Semiconductor Applications

Email: [email protected]

Board Rev

Project

Nov, 2012

B

B

28

12

Clock Generation

B

C5

0.1uF

R30

4.7k

R0603

J4

SMA

DNI

1

2

3

4

5

C17

0.1uF

R20

50

R0603

R18

0

R0603

C159

0.1uF

C147

0.1uF

C160

0.1uF

R219

4.7k

R0603

FB2

74279265

1

2

U4

ispCLOCK5304S

DI

BANK_0A

6

BANK_0B

8

VCCO_0

5

GNDO_0

7

VCCO_1

32

GNDO_1

30

BANK_1A

31

BANK_1B

29

VTT_REFA

13

REFA_REFP

14

REFSEL

19

RESET

20

REFB_REFN

15

VTT_REFB

16

LOCK

45

PLL_BYPASS

44

FBK

17

VTT_FBK

18

OEY

42

OEX

43

TDI

40

TMS

38

TCK

39

TDO

37

VCCD

21

VCCD

22

VCCA

46

VCCJ

41

GND

D

24

GND

D

48

GND

A

47

GND

D

23

NC_11

11

NC_12

12

NC_25

25

NC_26

26

NC_27

27

NC_28

28

NC_33

33

NC_34

34

NC_35

35

NC_36

36

NC_1

1

NC_2

2

NC_3

3

NC_4

4

NC_9

9

NC_10

10

R11

4.7k

R0603

R19

50

R0603

C141

0.1uF

R12

4.7k

R0603

SiT1602AC-11-25E-54.000000

X1

DI

PART_NUMBER = SiT1602AC-11-25E-54.000000

Manufacturer = SiTime

EOH

1

GND

2

VCC

4

OUTPUT

3

C9

330pF

C0402

C148

0.1uF

C6

0.01uF

PCI Express Board