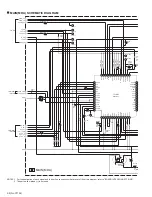

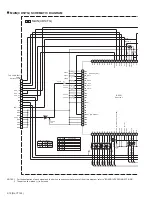

2-15(No.YF124)

DCO2

TL3201

REG_4.8V

L3203

NQR0602-001X

DCO1

DYO1

VC1

CLK27A

DCO0

L3204

10

µ

L3201

NQR0602-001X

OSD_HD

VOI_CLK

DYO2

DOT_CLK

T_F_V_RST

ASPECT

C3206

0.01

VC0

R3201 100

DCO3

T

C3204

10/6.3

VC3

VIF_CS

VOI_IN

DYO3

ANA_IN_H

GND

REG_3.1V

OUTH

VOI_OUT

BLKB

PSCTL

REG_1.7V

L3202

NQR0602-001X

BLKA

C3207

0.01

C3202

0.1

BLKC

C3203

0.1

VC2

R3208

820

DYO0

OUTV

OSD_VD

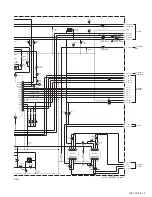

IC3201

JCP8055FP-2

1 HDCVF

2 VDCVF

3 CSYNC

4 VDOUT

5 SCANMODE

6 VDD(C)

7 VSS

8 RESVD

9 RESHD

10 SDOUT

11 SDIN

12 SCLK

13 CS

14 VDD(I)

15 VSS

16 RST

17

CLK

18

VC0

19

VC1

20

VC2

21

VC3

22

BLK1

23

BLK2

24

BLK3

25

HDOUT

26

VSS

27

VDD(I)

28

CLKOSD

29

AVSS

30

AVDD

31

IREF2

32

CROUT

33

ABAR2

34

COMP2

35

CBOUT

36

VREF2

37

COUT

38

AVDD

39

AVSS

40

IREF1

41

YCOUT

42

ABAR1

43

COMP1

44

YSOUT

45

VREF1

46

AVSS

47

AVDD

48

SCANEN

49

AMUTE

50

HRP1

51

HRP2

52

CSI0

53

CSI1

54

CSI2

55

CSI3

56

ADDATEST

57

VDD(C)

58

VSS

59

YSI0

60

YSI1

61

YSI2

62

YSI3

63

INH

64

INV

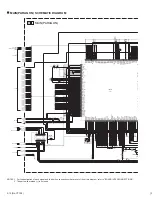

C3216

0.01

TL3202

T

C3205

47/6.3

TL3203

ASPECT

C3219

1

IC3202

MM3143BN-X

3.1V

1 VIN

2 GND

3 STBY

4

NC

5

VOUT

C3218

1

TO PARAGON

TO MAIN IF(CN104),

CPU,PARAGON

TO PARAGON

TO CPU

TO CPU,PARAGON

TO CPU

TO CPU,OP DRV

TO CPU

TO CPU,PARAGON

TO CPU

TO PARAGON

TO PARAGON

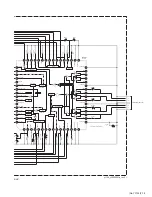

MAIN(VIDEO) SCHEMATIC DIAGRAM

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked ( ) is not used.