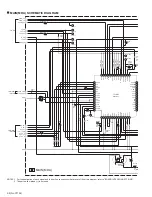

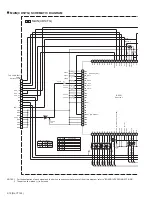

2-17(No.YF124)

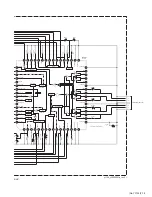

REC_CLK

REC_DATA

REF_CLK

REC_CTL

REC_ADJ

ATF_GAIN

RECH

PBH

HID

HID3

MONI_CHG

ENV_OUT

ATFI

ATFI

VRB_ATF

VRB_AGC

AGC_OUT

VREF_1.1

REG_2.5V

L3505

OPEN

L3503

NQR0602-001X

L3501

NQR0602-001X

GND

L3502

NQLC32M-100X

REG_4.8V

REG_3.1V

C3517

0.01

C3518

0.01

C3519

0.001

C3520

0.01

C3521

0.1

C3522

4.7

C3523

0.01

C3524

0.01

C3525

4.7

TL3501

CH

C3527

220p

1

ATF_GND

48

PB_MONI

49

PB_OUT

50

AGC_IN

51

AGC_CTL

52

AGC_DET

53

PB_GND

54

AGC_OUT

55

AGC_BUFF_I

56

REG_1.1V

57

AGC_BUFF_O

58

VRB_AGC

59

MAIN_GND

60

ATF_GAIN

61

VCA_OUT

62

ATF_IN

63

VRB_ATF

64

ATF_OUT

R3516

R3518

6.2k

R3517

56k

0

Ω

6dB

MAIN(PRE/REC)

1

0

TO PARAGON,REG

TO PARAGON

TO MAIN IF(CN102),

PARAGON

TO PARAGON

TO MAIN IF(CN102)

TO MAIN IF(CN102),

PARAGON

TO CPU

TO PARAGON

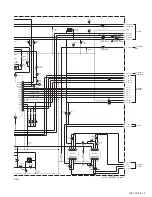

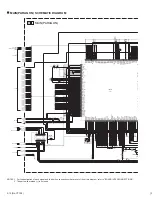

MAIN(PRE/REC) SCHEMATIC DIAGRAM

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked ( ) is not used.