CS4340

DS297PP3

13

3.

PIN DESCRIPTION

RST

1

Reset (

Input) - The device enters a low power mode and all internal state machines are reset to

the default settings when low. RST should be held low during power-up until the power supply,

master and left/right clocks are stable.

SDATA

2

Serial Audio Data (

Input) - Two’s complement MSB-first serial data is input on this pin. The

data is clocked into SDATA via the serial clock and the channel is determined by the Left/Right

clock. The required relationship between the Left/Right clock, serial clock and serial data is

defined by the DIF1-0 pins. The options are detailed in Figures 16-19.

SCLK

3

Serial Clock (

Input) - Clocks the individual bits of the serial data into the SDATA pin. The

required relationship between the Left/Right clock, serial clock and serial data is defined by the

DIF1-0 pins. The options are detailed in Figures 16-19.

The CS4340 supports both internal and external serial clock generation modes. Internal SCLK

mode is used to gain access to extra de-emphasis modes.

Internal Serial Clock Mode - In the Internal Serial Clock Mode, the serial clock is internally

derived and synchronous with the master clock and left/right clock. The SCLK/LRCK frequency

ratio is either 32, 48, or 64 depending upon the DIF1-0 pins as shown in Figures 16-19. Opera-

tion in this mode is identical to operation with an external serial clock synchronized with LRCK.

External Serial Clock Mode - The CS4340 will enter the External Serial Clock Mode whenever

16 low to high transitions are detected on the SCLK pin during any phase of the LRCK period.

The device will revert to Internal Serial Clock Mode if no low to high transitions are detected on

the SCLK pin for 2 consecutive periods of LRCK.

15

2

14

3

13

4

16

1

11

6

10

7

9

8

12

5

Reset

RST

MUTEC

Mute Control

Serial Data

SDATA

AOUTL

Left Analog Output

Serial Clock / De-emphasis SCLK/DEM1

VA

Analog Power

Left/Right Clock

LRCK

AGND

Analog Ground

Master Clock

MCLK

AOUTR

Right Analog Output

Digital Interface Format

DIF1

REF_GND Reference Ground

Digital Interface Format

DIF0

VQ

Quiescent Voltage

De-emphasis

DEM0

FILT+

Positive Voltage Reference

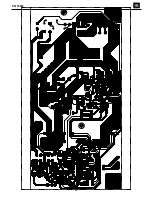

ES150PW

39

Содержание ES150PW

Страница 11: ...ES150PW 10...

Страница 14: ...ES150PW 13...

Страница 15: ...ES150PW 14...

Страница 16: ...ES150PW 15...

Страница 17: ...ES150PW 16...

Страница 21: ...ES150PW 20...

Страница 22: ...ES150PW 21...

Страница 23: ...2 1 3 2 1 3 ES150PW 22...

Страница 24: ...ES150PW 23...

Страница 25: ...ES150PW 24...

Страница 26: ...ES150PW 25...

Страница 27: ...ES150PW 26...

Страница 47: ...ES150PW 46...

Страница 49: ...2 3 1 TL072 U105 A VEE U105 D VDD U105 C 6 5 7 U105 B TL072 ES150PW 48...

Страница 50: ...Green Red D401 LED_5DIA ES150PW 49...

Страница 51: ...ES150PW 50...

Страница 52: ...ES150PW 51...

Страница 53: ...ES150PW 52...

Страница 54: ...ES150PW 53...

Страница 56: ...L01 56R 2 1 ES150PW 55...

Страница 59: ...ES150PW 58...