Everest CORE - Product Manual |

Application Guide

INGENIA | 08/01/2019

27

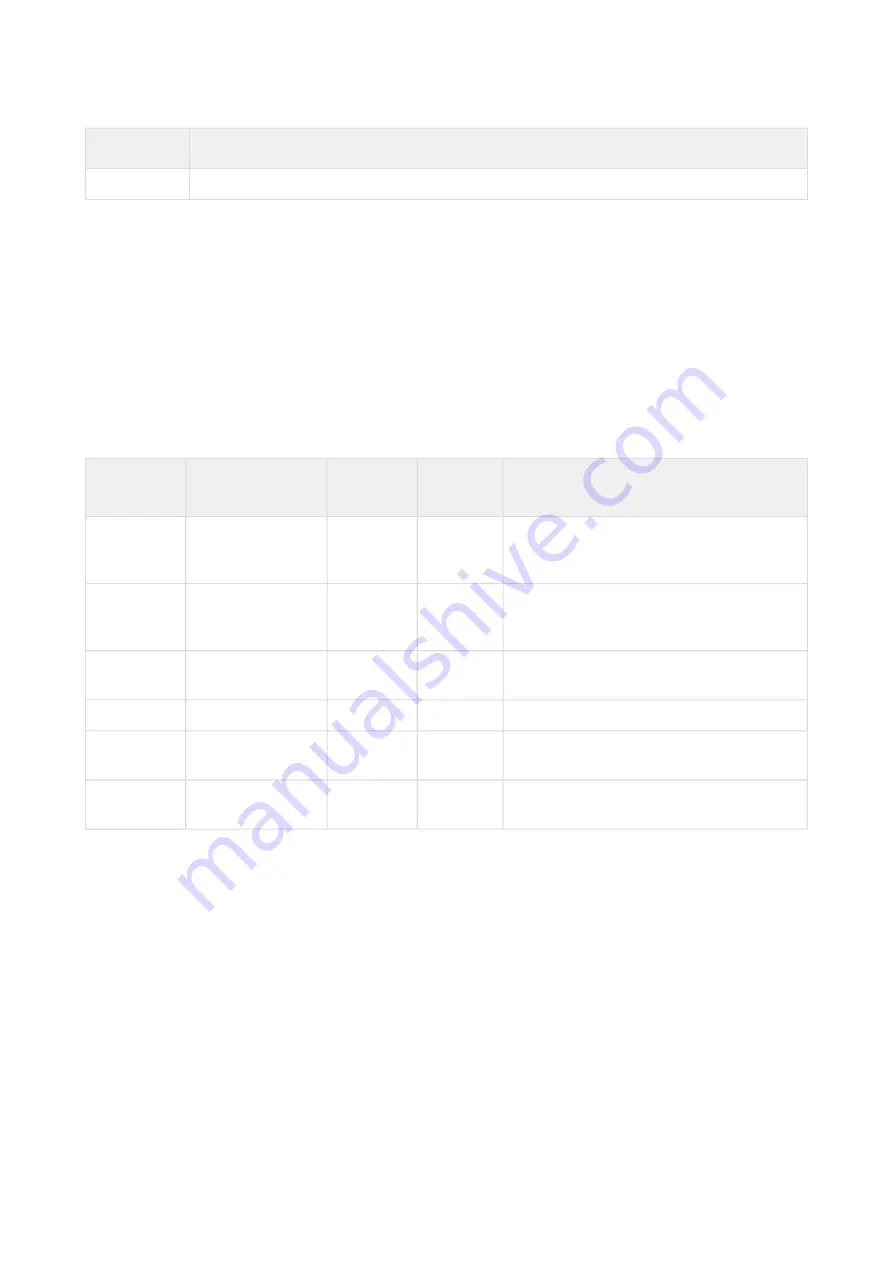

Signal

Description

GND_P

Internal DC bus reference voltage. To be connected to power pin 2 of P1 in Everest CORE

Design Notes

•

POW_SUP net would be connected to POW_SUP_S1 or POW_SUP_S2 depending on the line filter

implemented. If no line filter is on-board, it would be connected to POW.

•

Select a bidirectional TVS if an Inverse Polarity protection is implemented, and unidirectional TVS otherwise.

•

Selected TVS is rated 70 V standoff voltage instead of 80 V. About 1 mA will be sunk through it while the DC

bus is supplied to 80 V, but this should not entail a great power loss. On the other hand, by doing this the

lower maximum clamping voltage will result in a more effective protection for Everest CORE.

•

Electrolytic capacity would not be required in most cases.

•

Ceramic capacitors should be placed as close to the Everest as possible, being the closest the smallest in

capacity.

Bill of materials

Designator

Part Number

Manufactur

er

Package

Value / Description

C11, C12, C13

EKXG201ELL151ML2

5S

United

Chemi-Con

Radial,

Ø16x25

mm

Alimimium electrolytic capacitor, 150 µF, 200

V, -40 ºC ~105 ºC, MTBF 1000h @ 105 ºC, 1.89 A

@ 100 kHz current ripple

C14, C15,

C16, C17,

C18, C19

C5750X7S2A106K23

0KB

TDK

2220

Ceramic capacitor, 10 µF, 100 V, X7S

C20, C21,

C22, C23

C2012X7S2A105K12

5AE

TDK

0805

Ceramic capacitor, 1 µF, 100 V, X7S

C24, C25

HMK212B7104KG-T

TDK

0805

Ceramic capacitor, 100 nF, 100 V, X7R

D1

SMLJ70CA

Bourns

SMC /

DO-214-AB

Bidirectional diode TVS, 70 V standoff, 113 V

max. clamping, 3000 W

R1

V85MLA1210H

LittlelFuse

1210

Varistor, 85 V DC standoff, 250 A max. surge

current, 2.5 J max. surge energy

Logic supply

Here, it is assumed that a +5 V regulated supply is provided externally. There is a massive bunch of options to select

this component, and the best suited will probably be the one fitting the available power source from which to pick

the logic supply, whether it is AC or DC. In most cases, the power supply to feed the DC bus will also be the source

for the logic supply. In this case a DC/DC will be selected by matching its input voltage range to the maximum

expected voltage of the DC bus (including any possible re-injection). This DC/DC could be typically implemented

according to 3 approaches: a self-designed discrete DC/DC, an integrated module mounted into the PCB, or a

completely external DC/DC wired to the Interface Board. Any solution is valid, whenever the following is met: