Document Number: 002-10634 Rev. *J

Page

12 of 307

S6J3350 Series

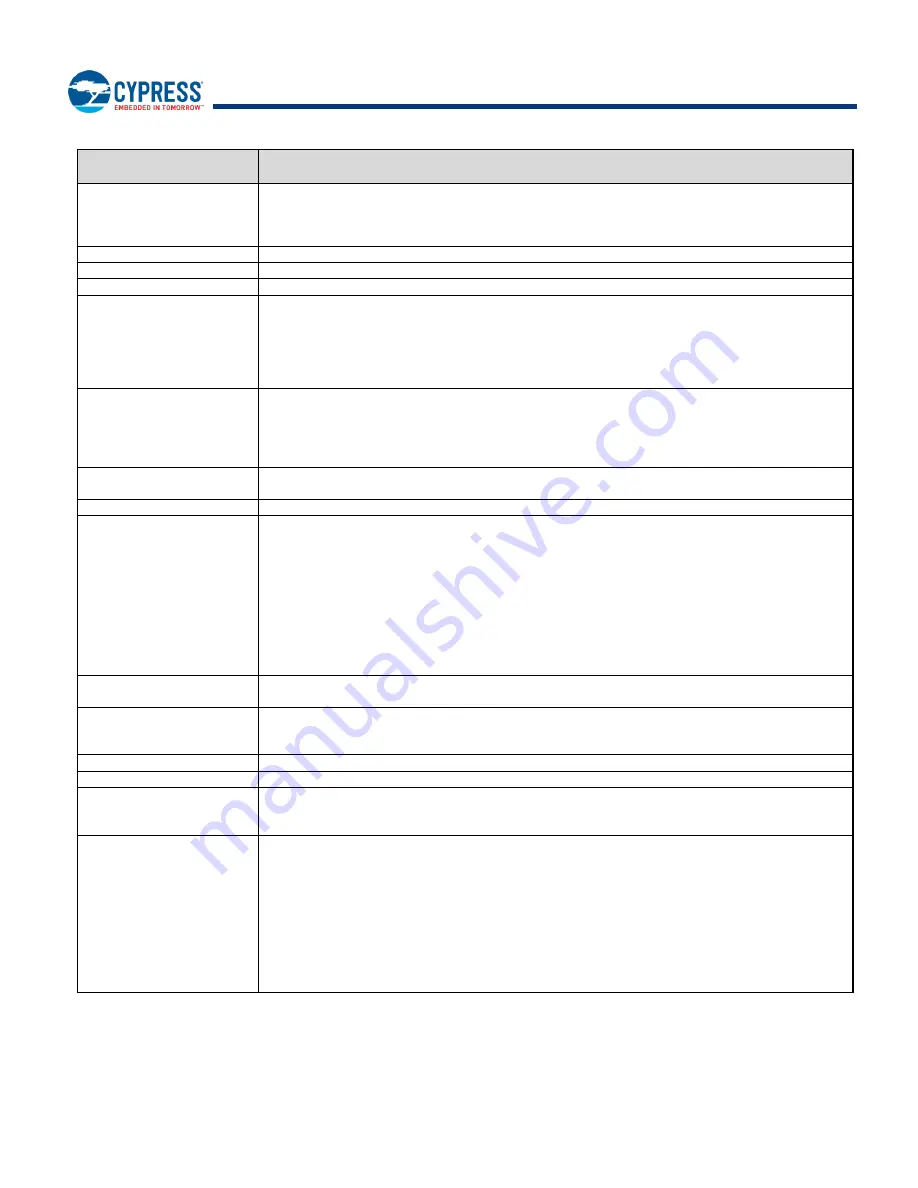

Feature

Description

Base Timer

See the Traveo™ Platform Hardware Manual in detail.

A unit consists of a pair of 16bit base timers. 32 units, that is, 64 channels of base timers are

available.

Reload Timer

See the Traveo™ Platform Hardware Manual in detail.

I/O Timer

See the Traveo™ Platform Hardware Manual in detail.

Up/Down Counter

See the Traveo™ Platform Hardware Manual in detail.

Multi-Functional Serial

(MFS)

See the Traveo™ Platform Hardware Manual in detail.

Only 2 ports of MFS have the dedicated I/O for I

2

C.

See I

2

The I

2

C is not designed to be hot swappable.

CTS/RTS is not mounted (hardware flow control is not supported for this series.)

CAN-FD

Flexible data rate is supported.

16 KB/ch of message RAM is available.

The clock output from CAN pre-scaler is supplied to every CAN. ECC error generation function

of the message RAM is not supported for this device. Therefore, CAN FD ECC Error Insertion

Control Register (FDFECR) is not writeable.

Real Time Clock (RTC)

with auto-calibration

See the Traveo

TM

Platform Hardware Manual in detail.

DDR High Speed SPI

ch.0: HSSPI as a MCU peripheral

Hyper BUS I/F

ch.0: Hyper Bus as a MCU peripheral

The following register is not supported and cannot be used.

−

Controller Status Register (HYPERBUSIn_CSR)

−

Interrupt Enable Register (HYPERBUSIn_IEN)

−

Interrupt Status Register (HYPERBUSIn_ISR)

−

Write Protection Register (HYPERBUSIn_WPR)

−

Test Register (HYPERBUSIn_TEST)

GPO signal can only be used for "Internal Control example by GPO" in this product, that is, it can

select using HyperBus of Traveo™ Platform Hardware Manual.

External Interrupt Capture

Unit (EICU)

See the Traveo

TM

Platform Hardware Manual in detail.

Ethernet AVB

10/100 Mbps

MII-Interface

Supports Audio-Video Bridging (AVB)

SHE

See the Traveo™ Platform Hardware Manual in detail.

Source Clock Timer

See the Traveo™ Platform Hardware Manual in detail.

External BUS

TEQFP208: 22 bit address and 16 bit data

TEQFP176: 22 bit address and 16 bit data

TEQFP144: 15 bit address and 8 bit data

Power Supply Control

(PSC)

PSC (PSC_1) output is used for external 1.2 V power supply module control and automatically

switched with the following condition.

"High": Request to supply VCC12

- "Power ON Reset" is released

- CPU wakes up from PSS shutdown mode

"Low": Request to stop supplying VCC12

- CPU transfers from RUN mode to PSS shutdown mode.

For timing chart of output signals include PSC in detail, see the "S6J3300 Hardware Manual"

and chapter "State Transition"