EM78P312N

8-Bit Microcontroller

28

•

Product Specification (V1.0) 10.03.2006

(This specification is subject to change without further notice)

5.7 UART (Universal Asynchronous Receiver/Transmitter)

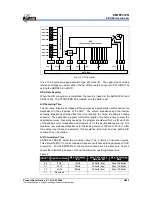

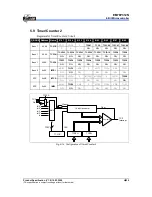

Registers for UART Circuit

R_BANK Address Name Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

URTD8 UMODE1 UMODE0 BRATE2 BRATE1 BRATE0 UTBE

TXE

Bank 2

0X05

URC1

R/W R/W R/W R/W R/W R/W R R/W

0 0

SBIM1 SBIM0

UINVEN

0 0 0

Bank 2

0X06

URC2

-- --

R/W R/W R/W

-- -- --

URRD8

EVEN PRE

PRERR OVERR FMERR

URBF RXE

Bank 2

0X07

URS

R/W R/W R/W R/W R/W R/W R R/W

URRD7 URRD6 URRD5 URRD4

URRD3

URRD2 URRD1 URRD0

Bank 2

0X08

URRD

R R R R R R R R

URTD 7 URTD 6

URTD 5

URTD 4 URTD 3 URTD 2 URTD 1 URTD0

Bank 2

0X09

URTD

W W W W W W W W

0

UERRIF

RBFF TBEF

TBIF

EXIF1 0 TCIF0

Bank 0

0x0F

ISFR2

--

R/W R/W R/W

R/W

R/W -- R/W

0

UERRIE

URIE UTIE

TBIE EXIE1 0 TCIE0

SFR 0x0F

IMR2

--

R/W R/W R/W

R/W

R/W -- R/W

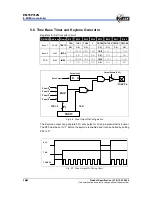

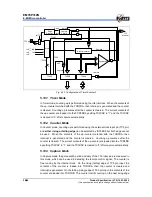

Baud rate

generator

Sele

cto

r

TC4

RX Control

TX Control

Interrupt

Control

RX shift register

URRD

URTD

URRD8

RX

TX

Parity control

Error flag

Data Bus

URTD8

RXE

TXE

UINVEN

UINVEN

Fsystem

Fig. 5-10 Function Block Diagram

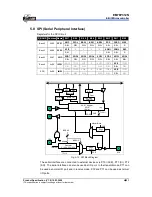

In Universal Asynchronous Receiver Transmitter (UART), each transmitted or received

character is individually synchronized by framing it with a start bit and stop bit.

Full duplex data transfer is possible since the UART has independent transmit and

receive sections. Double buffering for both sections allows the UART to be

programmed for continuous data transfer.