EM78P312N

8-Bit Microcontroller

Product Specification

(V1.0) 10.03.2006

•

11

(This specification is subject to change without further notice)

z

ISFR2 can be cleared by instruction, but cannot be set by instruction

z

IMR2 is the interrupt mask register

z

Note that reading ISFR2 will obtain the result of the ISFR2 "logic AND" and

IMR2

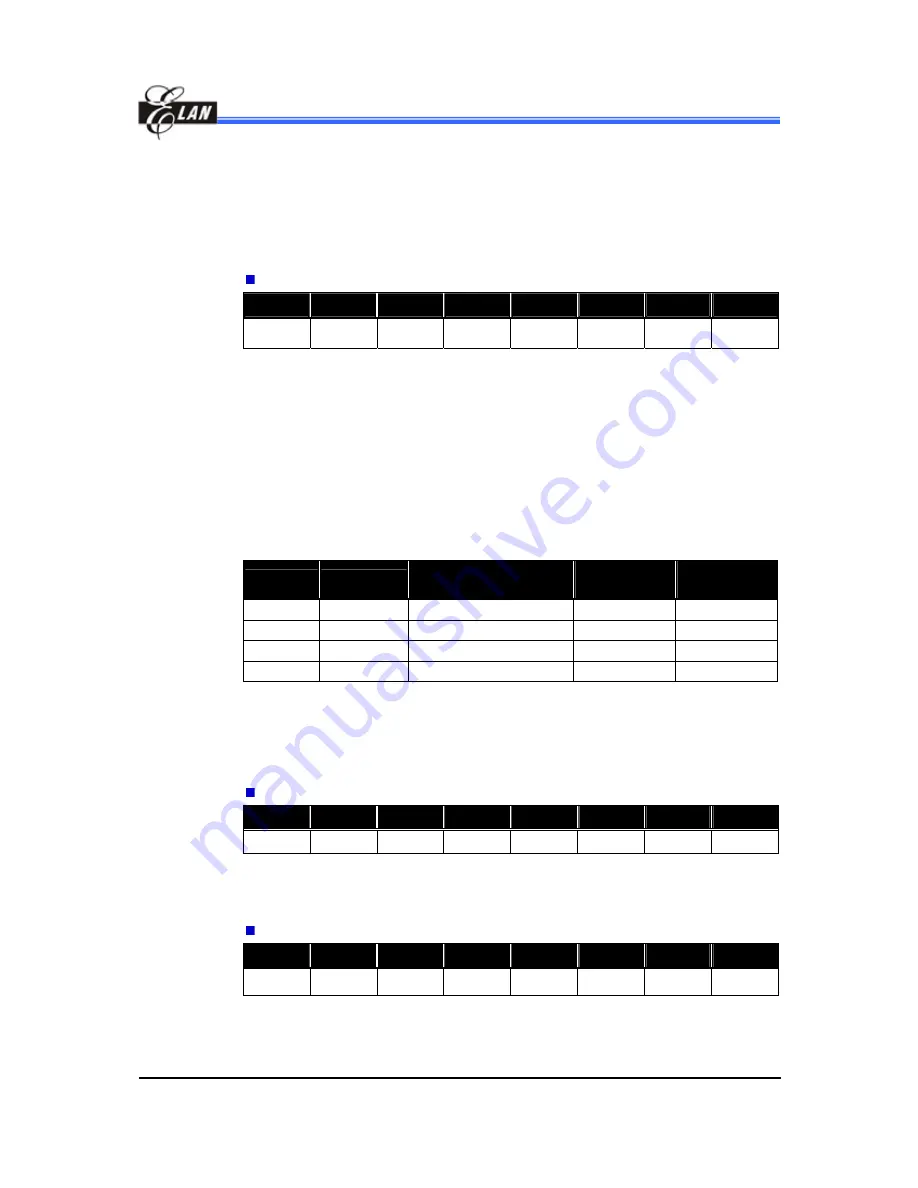

Bank 1 R5 TC3CR (Timer/Counter 3 Control Register)

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

TC3CAP

TC3S

TC3CK1

TC3CK0

TC3M

0 0 0

Bit 7 ( TC3CAP )

: Software capture control

TC3CAP = “0” :

-

TC3CAP = “1” :

Software capture

Bit 6 ( TC3S )

: Timer/Counter 3 start control

TC3S = “0” :

Stop and counter clear

TC3S = “1” :

Start

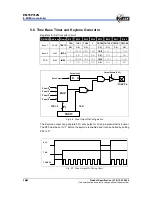

Bit 5 ~ Bit 4 ( TC3CK1 ~ TC3CK0 ) : Timer/Counter 3 Clock Source Select

TC3CK1

TC3CK0

Clock source

( Normal, Idle )

Resolution

( Fc=8M )

Max. time

( Fc=8M )

0 0

Fc/

2

12

512

μ

S 131.1mS

0 1

Fc/

2

10

128

μ

S 32.6mS

1 0

Fc/

2

7

16

μ

S 4.1mS

1

1

External clock (TC3 pin)

-

-

Bit 3 ( TC3M )

: Timer/Counter 3 mode select

TC3M = “0” :

Timer/Counter3 mode

TC3M = “1” :

Capture mode

Bank 1 R6 TC3DA (Timer 3 Data Buffer A)

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

TC3DA7 TC3DA6 TC3DA5 TC3DA4 TC3DA3 TC3DA2 TC3DA1 TC3DA0

Bit 7 ~ Bit 0 ( TC3DA7 ~ TC3DA0 )

: Data buffer of 8-bit Timer/Counter 3.

Reset does not affect this register.

Bank 1 R7 TC3DB (Timer 3 Data Buffer B)

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

TC3DB7 TC3DB6 TC3DB5 TC3DB4 TC3DB3 TC3DB2 TC3DB1 TC3DB0

Bit 7 ~ Bit 0 ( TC3DB7 ~ TC3DB0 ) :

Data buffer of 8-bit Timer/Counter 3

Reset does not affect this register.