Rev. 2.50

256

��ne 22� 20��

Rev. 2.50

25�

��ne 22� 20��

HT66F20/HT66F30/HT66F40/HT66F50/HT66F60

HT66FU30/HT66FU40/HT66FU50/HT66FU60

A/D Flash MCU with EEPROM

HT66F20/HT66F30/HT66F40/HT66F50/HT66F60

HT66FU30/HT66FU40/HT66FU50/HT66FU60

A/D Flash MCU with EEPROM

Address detect mode

Setting the Address Detect function enable control bit, ADDEN, in the UCR2 register, enables this

special function. If this bit is set to 1, then an additional qualifier will be placed on the generation

of a Receiver Data Available interrupt, which is requested by the RXIF flag. If the ADDEN bit

is equal to 1, then when the data is available, an interrupt will only be generated, if the highest

received bit has a high value. Note that the related interrupt enable control bit and the EMI bit of the

microcontroller must also be enabled for correct interrupt generation. The highest address bit is the

9th bit if the bit BNO=1 or the 8th bit if the bit BNO=0. If the highest bit is high, then the received

word will be defined as an address rather than data. A Data Available interrupt will be generated

every time the last bit of the received word is set. If the ADDEN bit is equal to 0, then a Receive

Data Available interrupt will be generated each time the RXIF flag is set, irrespective of the data last

but status. The address detect and parity functions are mutually exclusive functions. Therefore if the

address detect function is enabled, then to ensure correct operation, the parity function should be

disabled by resetting the parity function enable bit PREN to zero.

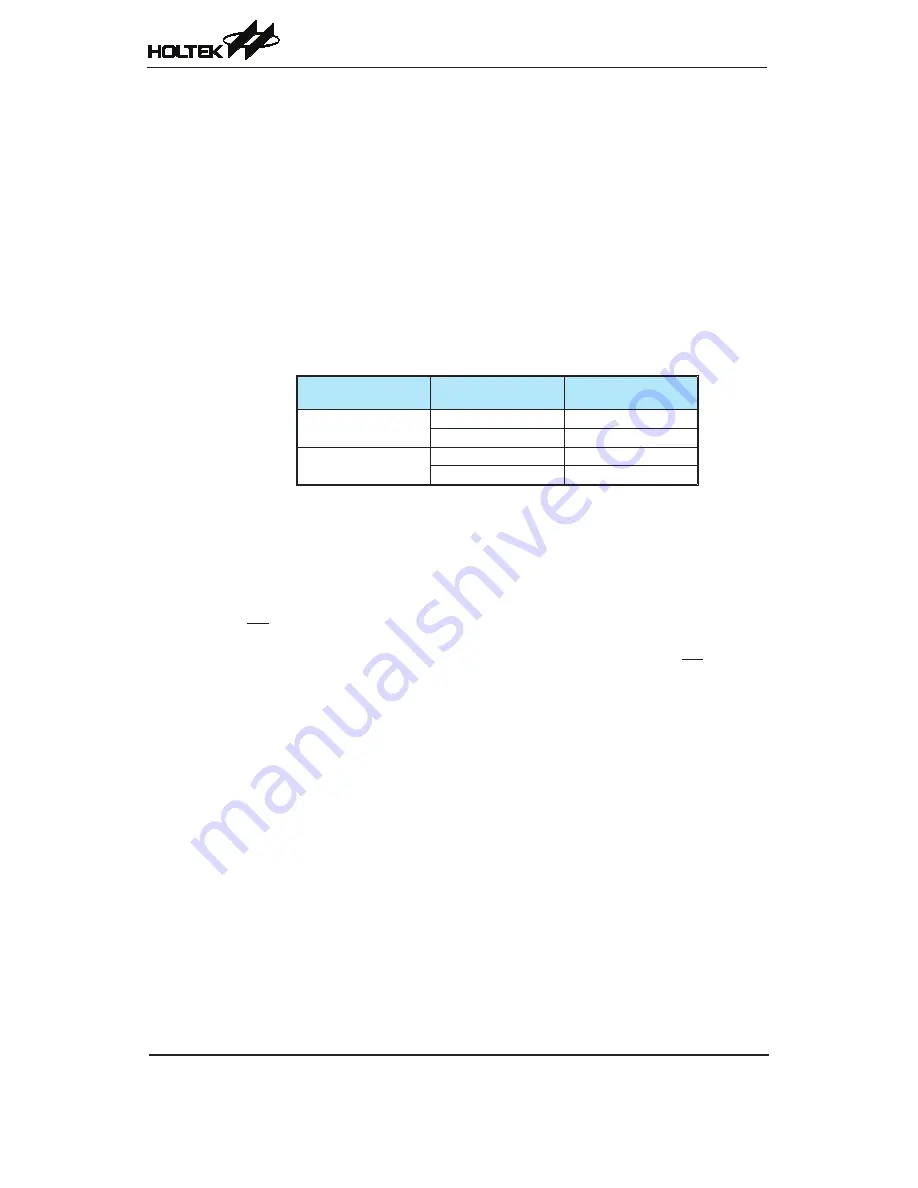

ADDEN

Bit 9 (BNO=1)

Bit 8 (BNO=0)

UART Interrupt

Generated

0

0

√

�

√

�

0

×

�

√

ADDEN Bit Function

UART Module Power-down and Wake-up

The MCU and UART Module are powered down independently of each other. The method of

powering down the MCU is covered in the previous MCU section of the datasheet. The UART

Module must be powered down before the MCU is powered down. This is implemented by first

clearing the UARTEN bit in the UCR1 register to disable the UART Module circuitry after which

the SCS internal line can be set high to disable the SPI interface circuits. When the UART and

SPI interfaces are powered down, the SCK and CLKI clock sources to the UART module will be

disabled. The UART Module can be powered up by the MCU by first clearing the SCS line to zero

and then setting the UARTEN bit. If the UART circuits is powered down while a transmission is still

in progress, then the transmission will be terminated and the external TX transmit pin will be forced

to a logic high level. In a similar way, if the UART circuits is powered down while receiving data,

then the reception of data will likewise be terminated. When the UART circuits is powered down,

note that the USR, UCR1, UCR2, UCR3, transmit and receive registers, as well as the BRG register

will not be affected.

The UART Module contains a receiver RX pin wake-up function, which is enabled or disabled by

the WAKE bit in the UCR2 register. If this bit, along with the UART enable bit named UARTEN,

the receiver enable bit named RXEN and the receiver interrupt enable bit named RIE, are all set

before the MCU and UART module are powered down, then a falling edge on the RX pin will wake

up the MCU from its power down condition. Note that as it takes a certain period of time known as

the System Start-up Time for oscillator to restart and stabilize after a wake-up, any data received

during this time on the RX pin will be ignored.

For a UART wake-up interrupt to occur, in addition to the bits for the wake-up enable control

and Receive interrupt enable control being set, the global interrupt enable control and the related

interrupt enable control bits must also be set. If these two bits are not set, then only a wake-up event

will occur and no interrupt will be serviced. Note also that as it takes a period of delay after a wake-

up before normal microcontroller resumes, the relevant UART interrupt will not be serviced until

this period of delay time has elapsed.