APEX

™

Exciter Incorporating FLO

™

Technology

Theory of Operation

APEX Exciter Digital Assembly Overview

Page: 4-6

888-2604-001

03/08/07

WARNING: Disconnect primary power prior to servicing.

4.3.2.1

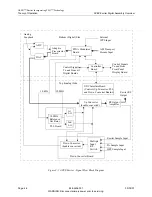

44.4 MHz Phase Lock Loop

A PLL is used to generate the 44.4 MHz clock signal for the modulator tray. It is

phase-locked to the 10 MHz reference signal. The 44.4 clock is divided by 4 to produce the

11.1 MHz clock, see Figure 4-3 for a block diagram of the 44.4 MHz phase lock loop.

Figure 4-3 The 44.4 MHz Phase Lock Loop

4.3.3

Exciter Output Spectral Response, RTAC Bypassed

Figure 4-4 shows the exciter output spectral response with RTAC bypassed. The modulator

bandwidth, in the Setup > Flo FPGA > FPGA Configure 4/5 screen, is set to 6 MHz. The

available bandwidth settings are 5, 6, 7, and 8 MHz. For each setting, the actual signal

bandwidth is approximately 0.5 MHz less than the indicated bandwidth, the actual

bandwidth for each setting is listed in Table 4-1.

In Figure 4-4, the skirts of the response drop rapidly, then the slope suddenly becomes

more gradual. This is the point where the intermodulation products start to appear in the

output. This point is called the shoulder. The shoulder level should be at lest -38 dB with

respect to the center of the response.

The output consists of multiple, closely spaced, modulated sub carriers. For Example, 4000

sub carriers are used in the 6 MHz bandwidth setting.

Table 4-1 Output Signal Bandwidth

Bandwidth

Setting

Actual

Bandwidth

5 MHz

4.52 MHz

6 MHz

5.42 MHz

7 MHz

6.33 MHz

8 MHz

7.23 MHz

÷

R

÷

N

Phase

Detector

44.4 MHz

VCO

÷

4

10 MHz

Reference

44.4 MHz

Clock

11.1 MHz

Clock

Oscillator

(From PLL

Board)