455

APPENDIX C Pin Status in Each CPU State

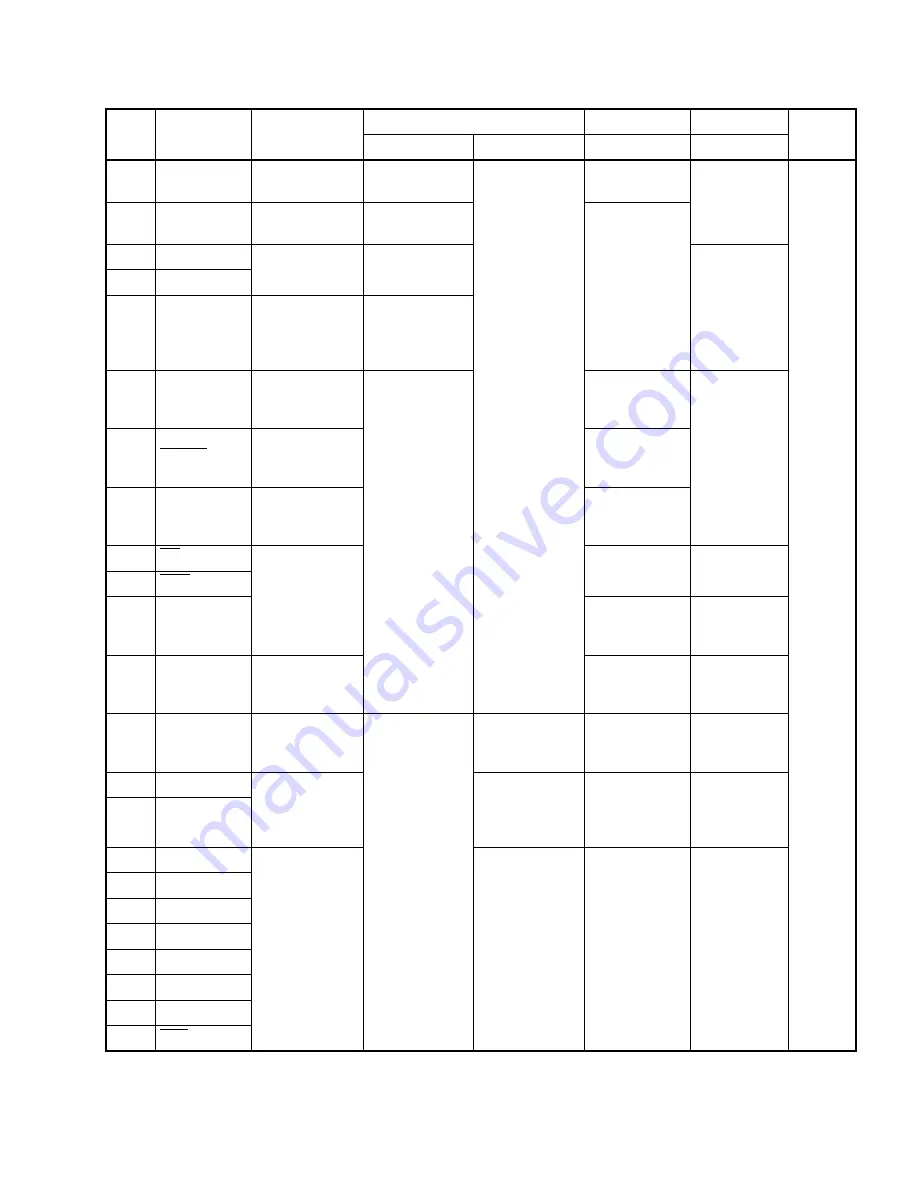

Table C-3 Pin status in external bus 8-bit mode

Pin

name

Function

In sleep mode

In stop mode

Bus release

At reset

Remarks

HIZX=0

HIZX=1

(BGRNT=1)

(RST=1)

P20-7

Port

Last status

retained

Last status

retained

Output Hi-Z or

keep the input at

0

Last status

retained

Output Hi-Z or

enable all-pin

input

-

P30-7

D24-31

Output retained

or Hi-Z

Output retained

or Hi-Z

Output Hi-Z

P40-7

A0-7

Output enabled

(Address output)

Output enabled

(Address output)

FF

H

output

P50-7

A8-15

P60-7

A16-23/

P: Last status

retained

F: Address

output

P: Last status

retained

F: Address

output

P80

RDY

P: Last status

retained

F: RDY input

Output Hi-Z or

keep the input at

0

P: Last status

retained

F: RDY input

Output Hi-Z or

enable all-pin

input

P81

BGRNT

P: Last status

retained

F: H output

L output

P82

BRQ

P: Last status

retained

F: BRQ input

BRQ input

P83

RD

Last status

retained

Output Hi-Z

H output

P84

WR0

P85

Port

Last status

retained

Output Hi-Z or

enable all-pin

input

P86

CLK

P: Last status

retained

F: CLK output

CLK output

CLK output

PC0-3 INT0-3

Last status

retained

Input enabled

Input enabled

Last status

retained

Output Hi-Z or

enable all-pin

input

PC4

INT4/CS0

P: Last status

retained

F: CS output

Output Hi-Z

Input enabled

Last status

retained

Hi-Z for CS

output

CS output

PC5-7 INT5-7/CS1-3

PD0

AIN0/INT8

Last status

retained

Input enabled

Last status

retained

Output Hi-Z or

enable all-pin

input

PD1

BIN0/INT9

PD2

AIN1/INT10

PD3

BIN1/INT11

PD4

ZIN0/INT12

PD5

ZIN1/INT13

PD6

DEOP2/INT14

PD7

ATG/INT15

Содержание MB91150 Series

Страница 1: ......

Страница 2: ......

Страница 3: ...FUJITSU LIMITED FR30 32 BIT MICROCONTROLLER MB91150 Series HARDWARE MANUAL ...

Страница 4: ......

Страница 10: ...vi ...

Страница 112: ...96 CHAPTER 3 MEMORY SPACE CPU AND CONTROL UNIT ...

Страница 174: ...158 CHAPTER 5 I O PORTS Note DDRI bit 6 is a test bit Always set the bit to 0 The value read from this bit is always 0 ...

Страница 178: ...162 CHAPTER 5 I O PORTS ...

Страница 214: ...198 CHAPTER 7 16 BIT RELOAD TIMER ...

Страница 240: ...224 CHAPTER 8 PPG TIMER ...

Страница 310: ...294 CHAPTER 13 8 10 BIT A D CONVERTER ...

Страница 318: ...302 CHAPTER 14 8 BIT D A CONVERTER ...

Страница 362: ...346 CHAPTER 15 UART ...

Страница 420: ...404 CHAPTER 19 PERIPHERAL STOP CONTROL ...

Страница 428: ...412 CHAPTER 20 CALENDAR MACROS ...

Страница 503: ...487 INDEX INDEX The index follows on the next page This is listed in alphabetic order ...

Страница 510: ...494 INDEX ...

Страница 512: ......