14. How to use

RX4111CE

Jump to

ETM62E-02

Seiko Epson Corporation

49

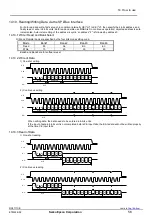

2) TSCLR bit (Time Stamp Clear)

Initialization of Bank3 6h

Table 64 TSCLR bit

TSCLR

Data

Description

Write

0

No operation

1

Initialize Bank3 6h.

TSEMP: 1, TSFUL: 0, TSAD2,1,0: (1,1,1)

EISEL bit (Enable Interrupt Select)

Enable/Disable control of interrupt is output when 8-time stamp data becomes full.

Table 65 EISEL bit (Event Interrupt Select)

EISEL

Data

Description

Write

0

Each event makes interrupt output respectively from /INT.

1

In case of 8-time stamp full recording, interrupt output from /INT.

Even SPI-Bus command trigger is executed, it makes no interrupt output.

1) TSFUL bit (Time Stamp Full)

8-time stamp data area full recording

Table 66 TSFUL bit

TSFUL

Data

Description

Read

0

Time stamp RAM area is not full.

1

8 times of time stamp recording area is fully recorded.

2) TSEMP bit (Time Stamp Empty)

No recording date in RAM.

Table 67 Time Stamp Empty bit

TSEMP

Data

Description

Read

0

There is some data.

1

There is no data.

TSAD2, TSAD1, TSAD0 bit (Time Stamp Address pointer)

T

he latest address pointer time stamped recorded in RAM

Table 68 TSAD bit

TSAD2, 1, 0

TSAD2

TSAD1

TSAD0

Address pointer

Read

0

0

0

Bank4 0h - 7h

0

0

1

Bank4

8h - Fh

0

1

0

Bank5

0h - 7h

0

1

1

Bank5

8h - Fh

1

0

0

Bank6

0h - 7h

1

0

1

Bank6

8h - Fh

1

1

0

Bank7

0h - 7h

1

1

1

Bank7

8h - Fh, default