RX

-

8581

SA

/

JE

/

NB

Page - 10

MQ372-02

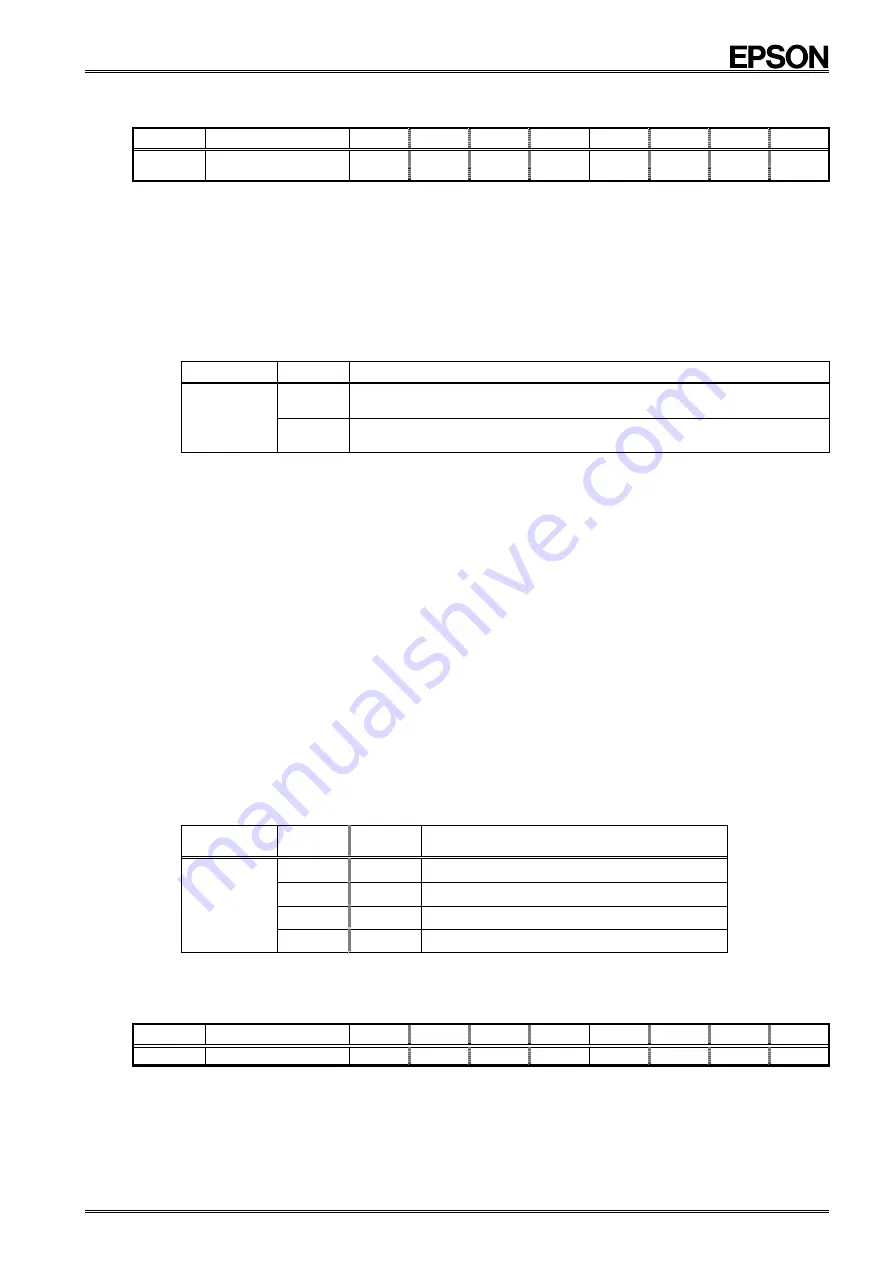

8.2.4. Extension register (Reg-D)

Address

Function

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

Extension Register

TEST

WADA

USEL

TE

!

!

TSEL1

TSEL0

D

(Default)

(0)

(

−

)

(

−

)

(

−

)

(0)

(0)

(

−

)

(

−

)

∗

1)

The default value is the value that is read (or is set internally) after powering up from 0 V.

∗

2)

"o" indicates write-protected bits. A zero is always read from these bits.

∗

3)

"

−

" indicates a default value is undefined.

•

This register is used to specify the target for the alarm function or time update interrupt function and to select or

set operations such as fixed-cycle timer operations.

1) TEST bit

This is the manufacturer's test bit. Its value should always be "0".

Be careful to avoid writing a "1" to this bit when writing to other bits.

∗

If a "1" is inadvertently written to this TEST bit, there is a safety function where by this bit will be automatically cleared to zero when a STOP

condition or Repeated START condition is received or when the 0.95-second bus timeout function operates.

TEST

Data Description

0

Normal operation mode

∗

Default

Write/Read

1

Setting prohibited (manufacturer's test bit)

2) WADA (Week Alarm/Day Alarm) bit

This bit is used to specify either WEEK or DAY as the target of the alarm interrupt function.

Writing a "1" to this bit specifies DAY as the comparison object for the alarm interrupt function.

Writing a "0" to this bit specifies WEEK as the comparison object for the alarm interrupt function.

∗

For details, see "8.5. Alarm Interrupt Function".

3) USEL (Update Interrupt Select) bit

This bit is used to specify either "second update" or "minute update" as the update generation timing of the time

update interrupt function.

Writing a "1" to this bit specifies the internal clock's "minute update" (once per minute) operation as the timing

by which time update interrupts are generated.

Writing a "0" to this bit specifies the internal clock's "second update" (once per second) operation as the timing

by which time update interrupts are generated.

∗

For details, see "8.4. Time Update Interrupt Function".

4) TE (Timer Enable) bit

This bit controls the start/stop setting for the fixed-cycle timer interrupt function.

Writing a "1" to this bit specifies starting of the fixed-cycle timer interrupt function (a countdown starts from a

preset value).

Writing a "0" to this bit specifies stopping of the fixed-cycle timer interrupt function.

∗

For details, see "8.3. Fixed-cycle Timer Interrupt Function".

5) TSEL0,1 (Timer Select 0, 1) bits

The combination of these two bits is used to set the countdown period (source clock) for the fixed-cycle timer

interrupt function (four settings can be made).

TSEL0,1

TSEL1

(bit 1)

TSEL0

(bit 0)

Source clock

0 0

4096

Hz

/Once per 244.14

µ

s

0

1

64 Hz

/ Once per 15.625 ms

1

0

"Second" update

/Once per second

Write/Read

1

1

"Minute" update

/Once per minute

∗

For details, see "8.3. Fixed-cycle Timer Interrupt Function".

8.2.5. RAM register (Reg - 7)

Address

Function

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

7

RAM

•

•

•

•

•

•

•

•

•

This RAM register is read/write accessible for any data in the range from 00

h to FF

h.