6: The Bus Interface

6-4

EPSON

ARM720T CORE CPU MANUAL

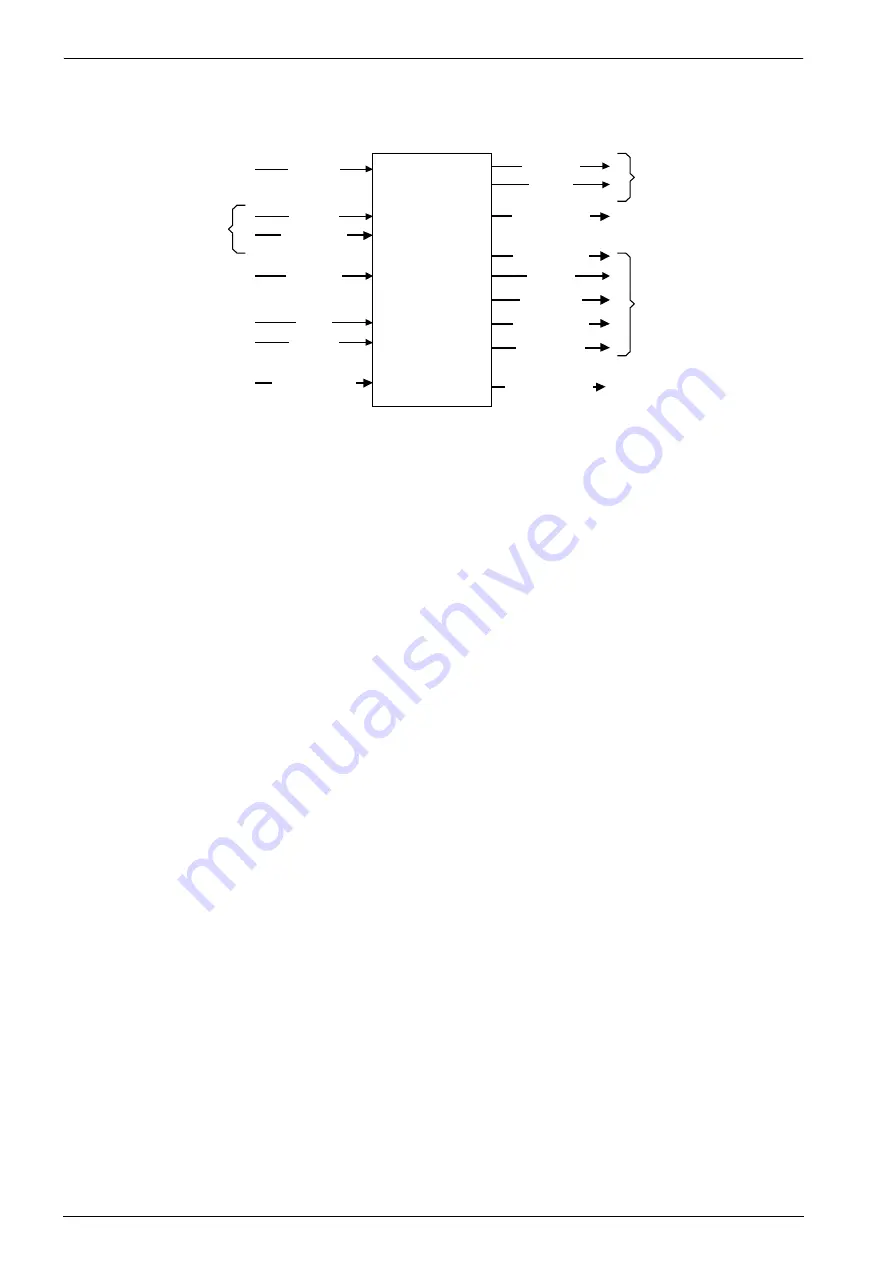

The AHB bus master interface signals are shown in Figure 6-2.

Figure 6-2 AHB bus master interface

A HB master

HBUSREQ

HLOCK

HREADY

HRESETn

HWRITE

HCLKEN

HCLK

HTRANS[1:0]

HRDATA[31:0]

HWDATA[31:0]

HPROT[3:0]

HBURST[2:0]

HSIZE[2:0]

HADDR[31:0]

HRESP[1:0]

HGRANT

A rbiter grant

Data

Reset

Clock

Transf er type

Data

A ddress

and control

A rbiter

Transf er

response

Содержание ARM720T Core cpu

Страница 4: ......

Страница 12: ...CONTENTS viii EPSON ARM DDI 0229B THIS PAGE IS BLANK ...

Страница 13: ...Preface ...

Страница 14: ......

Страница 18: ...Preface xiv EPSON ARM720T CORE CPU MANUAL THIS PAGE IS BLANK ...

Страница 19: ...1 Introduction ...

Страница 20: ......

Страница 39: ...2 Programmer s Model ...

Страница 40: ......

Страница 58: ...2 Programmer s Model 2 18 EPSON ARM720T CORE CPU MANUAL THIS PAGE IS BLANK ...

Страница 59: ...3 Configuration ...

Страница 60: ......

Страница 70: ...3 Configuration 3 10 EPSON ARM720T CORE CPU MANUAL THIS PAGE IS BLANK ...

Страница 71: ...4 Instruction and Data Cache ...

Страница 72: ......

Страница 75: ...5 Write Buffer ...

Страница 76: ......

Страница 79: ...6 The Bus Interface ...

Страница 80: ......

Страница 94: ...6 The Bus Interface 6 14 EPSON ARM720T CORE CPU MANUAL THIS PAGE IS BLANK ...

Страница 95: ...7 Memory Management Unit ...

Страница 96: ......

Страница 118: ...7 Memory Management Unit 7 22 EPSON ARM720T CORE CPU MANUAL THIS PAGE IS BLANK ...

Страница 119: ...8 Coprocessor Interface ...

Страница 120: ......

Страница 131: ...9 Debugging Your System ...

Страница 132: ......

Страница 177: ...10 ETM Interface ...

Страница 178: ......

Страница 182: ...10 ETM Interface 10 4 EPSON ARM720T CORE CPU MANUAL THIS PAGE IS BLANK ...

Страница 183: ...11 Test Support ...

Страница 184: ......

Страница 198: ...11 Test Support 11 14 EPSON ARM720T CORE CPU MANUAL THIS PAGE IS BLANK ...

Страница 199: ...Appendix A Signal Descriptions ...

Страница 200: ......

Страница 208: ...A Signal Descriptions A 8 EPSON ARM720T CORE CPU MANUAL THIS PAGE IS BLANK ...

Страница 209: ...Glossary ...

Страница 210: ......

Страница 217: ...Index ...

Страница 218: ......