This document is the ownership of EMAC, Inc. Copyright 2003. Unauthorized duplication or copying of this document is strictly forbidden.

iPac HCS12 Manual.doc

- 6 -

Rev 1.2 - 11/11/03

2.5 PLD Based General Purpose Digital I/O

These input and output lines provide connections for heavier industrial relays and switches. They are connected to the PLD

of the iPac HCS12 with the exception of lines PE0 – PE4 which are connected directly to the processor. These 5 lines with

the addition of PZ0 – PZ2 make up a dedicated input port whose input lines should not exceed 5 Vdc. The dedicated output

port lines PY0 – PY7 can drive 25 ma. loads. The open collector high drive output port PX0 – PX7 has drive 500 ma. sink

drive capability and a maximum total I/O drive of 1500 ma. for these 8 lines.

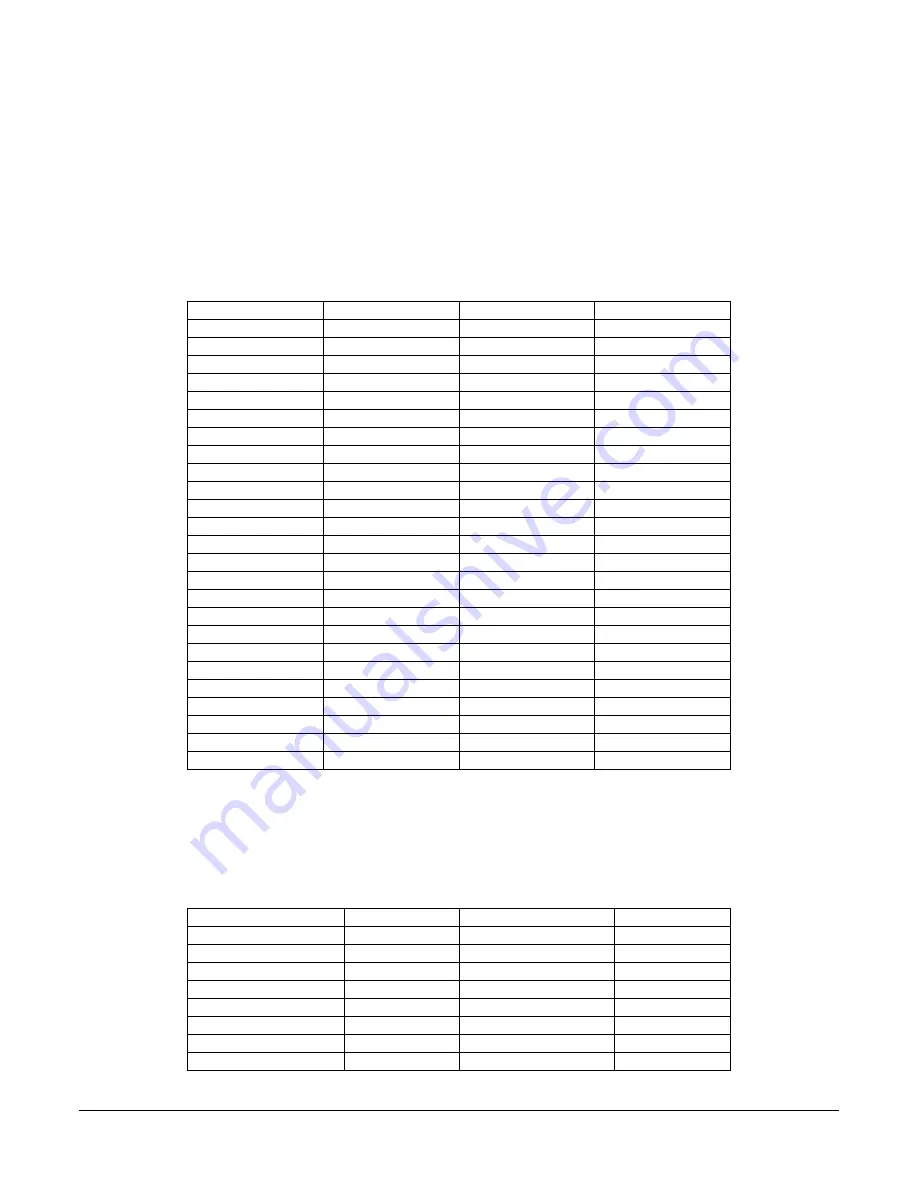

Table 3: PLD BASED DIGITAL I/O Connector (HDR1)

Pin

Signal

Pin

Signal

1

PY7

2

GND

3

PY6

4

GND

5

PY5

6

GND

7

PY4

8

GND

9

PY3

10

GND

11

PY2

12

GND

13

PY1

14

GND

15

PY0

16

GND

17

PX7

18

GND

19

PX6

20

GND

21

PX5

22

GND

23

PX4

24

GND

25

PX3

26

GND

27

PX2

28

GND

29

PX1

30

GND

31

PX0

32

GND

33

PZ2

34

GND

35

PZ1

36

GND

37

PZ0

38

GND

39

PE4

40

GND

41

PE3

42

GND

43

PE2

44

GND

45

PE1

46

GND

47

PE0

48

GND

49

5V(Vcc)

50

GND

The PLD is connected to the HCS12 processor using pseudo data bus comprised of the processor’s port lines. Table 4 defines

these port line assignments. To access PLD Port X, perform a write with A0 = 0. To access PLD Port Y, perform a write with

A0 = 1. To access PLD Port Z, perform a read with A0 = 0.

Table 4: PLD PSUEDO DATA BUS PORT LINE ASSIGNMENTS

Processor Port Line

Description

Processor Port Line

Description

PB0

DBUS 0

PJ0

DBUS A0

PB1

DBUS 1

PJ1

R/*W

PB2

DBUS 2

PJ7

PLD *CS

PB3

DBUS 3

PB4

DBUS 4

PB5

DBUS 5

PB6

DBUS 6

PB7

DBUS 7