CS5521 CS5523

DS317PP2

23

differential output voltage of the amplifier must not

exceed 2.8 V. The equation

ABS(VIN + VOS) x 20 = 2.8 V

defines the differential output limit, where

VIN = (AIN+) - (AIN-)

is the differential input voltage and VOS is the ab-

solute maximum offset voltage for the instrumenta-

tion amplifier (VOS will not exceed 40 mV). If the

differential output voltage from the amplifier ex-

ceeds 2.8 V, the amplifier may saturate, which will

cause a measurement error.

The input voltage into the modulator must not

cause the modulator to exceed a low of 20 percent

or a high of 80 percent 1’s density. The nominal full

scale input span of the modulator (from 30 percent

to 70 percent 1’s density) is determined by the

VREF voltage divided by the Gain Factor. See Ta-

ble 6 to determine if the CS5521/23 are being used

properly. For example, in the 55 mV range, to de-

termine the nominal input voltage to the modulator,

divide VREF (2.5 V) by the Gain Factor (2.2727).

When a smaller voltage reference is used, the re-

sulting code widths are smaller causing the con-

verter output codes to exhibit more changing codes

for a fixed amount of noise. Table 6 is based upon

a VREF = 2.5 V. For other values of VREF, the val-

ues in Table 6 must be scaled accordingly.

Figures 8 and 9 illustrate the input models for the

AIN and VREF pins. The dynamic input current for

each of the pins can be determined from the models

shown and is dependent upon the setting of the

CFS1 and CFS0 (Chop Frequency Select) bits. The

effective input impedance for the AIN+ and AIN-

pins remains constant for the three low level mea-

surement ranges (25 mV, 55 mV, and 100 mV).

The input current is lowest with the CFS bits

cleared to logic 0s.

Note: Residual noise appears in the converter’s baseband for

output word rates greater than 61.6 Hz if the CFS bits are

logic 0. To eliminate the residual noise for word rates of 61.6

Hz and lower, 256 Hz chopping is recommended, and for 84.5

Hz and 101.1 Hz filters, 4096 Hz chopping is recommended.

Note that C=48pF is for input current modeling only. For

physical input capacitance see ‘Input Capacitance’ specifica-

tion under ‘Analog Characteristics’ on page 3.

Charge Pump Drive

The CPD (Charge Pump Drive) pin of the converter

can be used with external components (shown in

Figure 1) to develop an appropriate negative bias

voltage for the NBV pin. When CPD is used to gen-

erate the NBV, the NBV voltage is regulated with

an internal regulator loop referenced to VA+.

Therefore, any change on VA+ results in a propor-

Note:

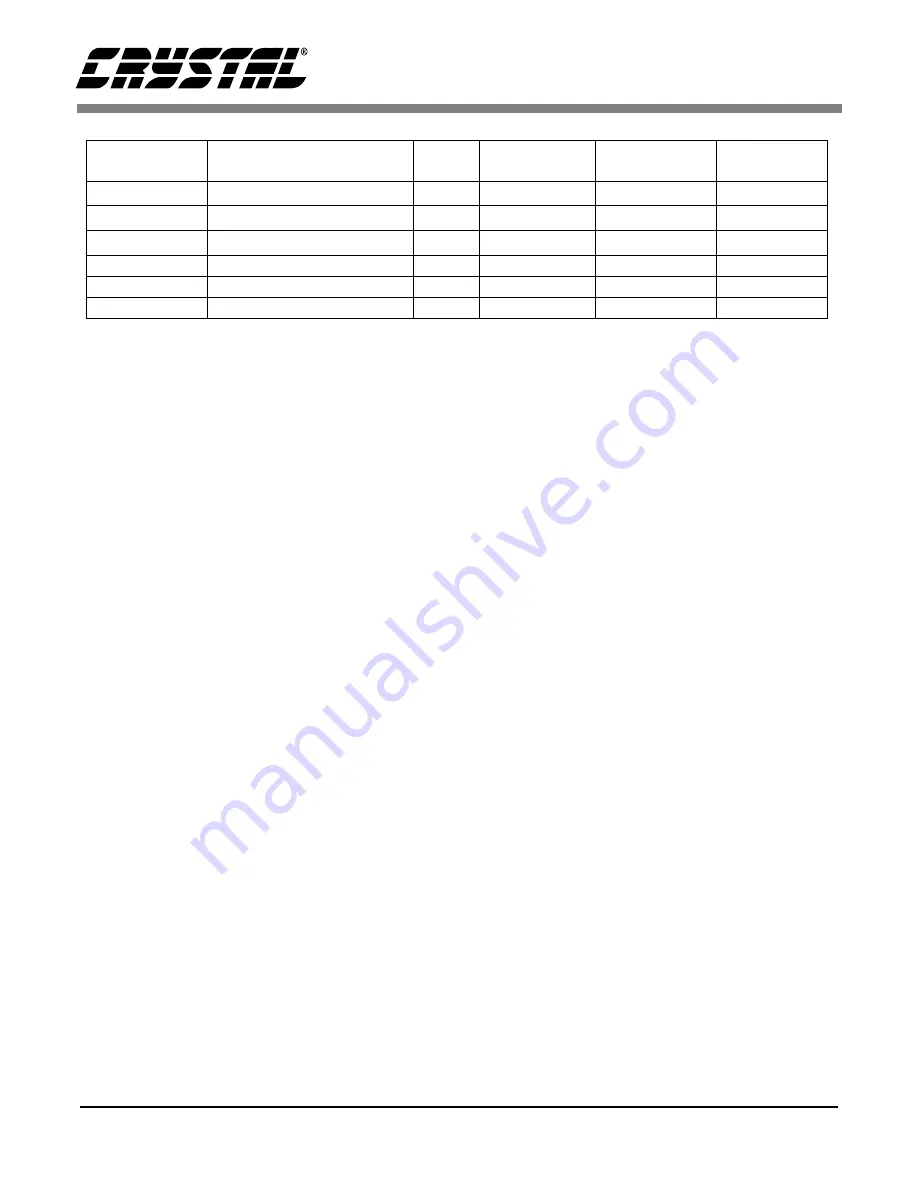

1. The converter’s actual input range, the delta-sigma’s nominal full scale input, and the delta-sigma’s

maximum full scale input all scale directly with the value of the voltage reference. The values in the

table assume a 2.5 V VREF voltage.

2. The 2.8 V limit at the output of the 20X amplifier is the differential output voltage.

Input Range

(1)

Max. Differential Output

20X Amplifier

VREF

Gain Factor

∆

-

Σ

Nominal

Differential Input

∆

-

Σ

Max. Input

±

25 mV

2.8 V

2.5V

5

±

0.5 V

±

0.75 V

±

55 mV

2.8 V

2.5V

2.272727...

±

1.1 V

±

1.65 V

±

100 mV

2.8 V

2.5V

1.25

±

2.0 V

±

3.0 V

±

1.0 V

-

2.5V

2.5

±

1.0 V

±

1.5 V

±

2.5 V

-

2.5V

1.0

±

2.5 V

±

5.0 V

±

5.0 V

-

2.5V

0.5

±

5.0 V

0V, VA+

Table 6. Relationship between Full Scale Input, Gain Factors, and Internal Analog Signal Limitations