CDB4923 CDB49300

16

DS262DB2

7. INPUT

7.1

Analog Input

A stereo input is provided at RCA jacks J55 and

J56. These inputs are designed to accept a full-scale

signal of 2 V

rms

. Each single-ended signal is con-

verted to a differential 2 V

rms

signal before being

applied to the inputs of the CS5334 ADC. The

CS5334 and its analog input buffers can be found

in Figure 9.

The CS5334’s clock signals can be accessed at the

test points labeled ALG_MCLK, ALG_SCLK, and

ALG_LRCLK (these test points can be found in

Figure 11). The serial data stream coming from the

CS5334 can be probed at the 34SDATA test point

(TP22). Jumper J52 is used to configure the

CS5334 for slave or master mode. The default,

slave mode, is used when the CS5334 accepts all

clock signals from another source. When in master

mode, the CS5334 accepts MCLK and generates

SCLK and LRCLK. The CDB4923/300 is config-

ured to use the CS5334 in slave mode only. Please

contact the factory for details on how to use the

CS5334 in master mode.

The digital output format of the CS5334 can be

configured with switch S4 as described in Table 14.

More details on the CS5334 can be found in the

CS5334 datasheet.

7.2

Digital Input

There are two possible sources of digital audio for

the CDB4923/300: S/PDIF, and bursty delivery

from the host PC across the parallel interface.

Bursty delivery is accomplished by spooling a file

from the host PC to the CDB4923/300 using the

PARLLPLY.EXE program found on the included

floppy. Audio delivered across the S/PDIF inter-

face comes from a digital source such as a DVD

player.

The S/PDIF inputs are J30 (RCA) and J32 (Opti-

cal), and can be found in Figure 10. It is vital to

note, though, that only one of these S/PDIF inputs

can be used at any given time. The active jack is de-

termined by the setting of jumper J31 (S/PDIF IN).

When J31 is in the ’OPT’ position, S/PDIF data will

be accepted only from J32. When J31 is in the

’RCA’ position, S/PDIF data will be accepted only

from J30.

The S/PDIF signal is routed to the CS8414 receiver

(U13). The digital output format of the CS8414 is

configured using switch S1 as described in Table

15. The CDB4923/300 comes from the factory con-

figured to operate in I

2

S mode. Note that this de-

fault should not be changed unless the DSP has

been configured to use a different serial format.

Jumpers J65 and J66 control the SEL and

CS12/FCK pins of the CS8414. These pins can be

used to select what is displayed on the channel sta-

tus outputs of the Digital Audio Interface Receiver.

By default these pins are pulled up and the jumpers

are not stuffed. If the user wishes to change the val-

ues of these pins a stake header should be installed.

The CS8414, its control switch, and jumpers can be

found in Figure 10. If more details on the CS8414

are needed, please reference the CS8414 datasheet.

34DIF1

34DIF0

Digital Input Format

LO

LO

20-Bit Left Justified, Rising SCLK

LO

HI

20-Bit Left Justified, Falling SCLK

HI

LO

20 Bit I

2

S, Rising SCLK (default)

HI

HI

Power Down

Table 14. CS5334 Digital Output Formats (S4)

M2

M1

M0

Audio Serial Port Format

LO

LO

LO

Out, L/R, 16-24 Bits

LO

LO

HI

In, L/R, 16-24 Bits

LO

HI

LO

Out, L/R, I

2

S

LO

HI

HI

In, L/R, I

2

S (default)

HI

LO

LO

Out, WSYNC, 16-24 Bits

HI

LO

HI

Out, L/R, 16 Bits LSBJ

HI

HI

LO

Out, L/R, 18 Bits LSBJ

HI

HI

HI

Out, L/R, MSB Last

Table 15. Digital Output Format settings

for CS8414 (S1)

Содержание CS492 Series

Страница 18: ...CDB4923 CDB49300 18 DS262DB2 9 APPENDIX A SCHEMATICS Figure 4 CS492x CS493xx ...

Страница 19: ...CDB4923 CDB49300 DS262DB2 19 Figure 5 System Power ...

Страница 20: ...CDB4923 CDB49300 20 DS262DB2 Figure 6 PC Interface ...

Страница 21: ...CDB4923 CDB49300 DS262DB2 21 Figure 7 Control Logic ...

Страница 22: ...CDB4923 CDB49300 22 DS262DB2 Figure 8 Clocking ...

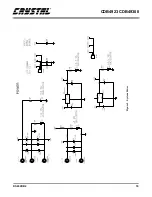

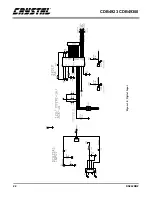

Страница 23: ...CDB4923 CDB49300 DS262DB2 23 Figure 9 Analog Input ...

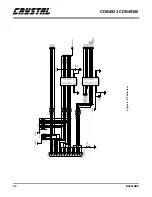

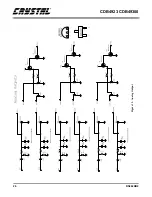

Страница 24: ...CDB4923 CDB49300 24 DS262DB2 Figure 10 Digital Input ...

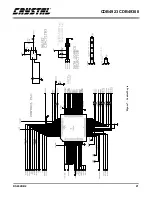

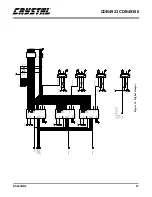

Страница 25: ...CDB4923 CDB49300 DS262DB2 25 Figure 11 D A Converters ...

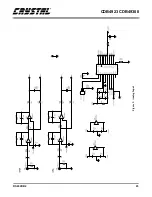

Страница 26: ...CDB4923 CDB49300 26 DS262DB2 Figure 12 Analog Output ...

Страница 27: ...CDB4923 CDB49300 DS262DB2 27 Figure 13 Digital Output ...

Страница 28: ...CDB4923 CDB49300 28 DS262DB2 Figure 14 Top Layer ...

Страница 29: ...CDB4923 CDB49300 DS262DB2 29 Figure 15 Bottom Layer ...

Страница 30: ...CDB4923 CDB49300 30 DS262DB2 Figure 16 SSTOP ...

Страница 31: ...CDB4923 CDB49300 DS262DB2 31 Figure 17 ASYSTOP ...

Страница 32: ...CDB4923 CDB49300 32 DS262DB2 Figure 18 Layer 2 ...

Страница 33: ...CDB4923 CDB49300 DS262DB2 33 Figure 19 Layer 3 ...

Страница 49: ... Notes ...

Страница 50: ......