CDB4923 CDB49300

8

DS262DB2

PSEL==1 when configuring for I

2

C mode because

PSEL and SCDIO are multiplexed onto the same

pin.

Two of the DSP jumpers are designed to act as cur-

rent measurement points for the CS492x/CS493xx.

Jumper J59 is the analog current measurement

point, and it must be installed for the PLL to func-

tion. Jumper J60 is the digital current measurement

point, and it must be installed in order to supply

power to the digital logic of the CS492x/CS493xx.

Jumper J1 is the clock selection jumper. When J1 is

in the ’CLKIN’ position, the clock present on pin 30

of the DSP (CLKIN) will drive the internal DSP

clocks directly. When J1 is in the ’PLL’ position,

the clock present at pin 30 is used as the reference

clock for the CS492x/CS493xx internal PLL. The

frequency required for the reference clock when

using the internal PLL is application code depen-

dent, so the relevant application code user’s guide

should be consulted to determine which frequency

to provide.

3.2

External Memory

Some CDB4923/300 boards may be shipped with

an external memory board. There two different ex-

ternal memory boards available:

•

CRD4923-MEM - external ROM for CS492x

•

CDB49300-MEM - external ROM and RAM

for CS493xx

The CS492x requires an external ROM for auto-

boot, and the CS4926 requires an external ROM

when processing DTS audio streams. The

CRD4923-MEM external memory board is tailored

for the CDB4923. The schematic for CRD4923-

MEM can be found in Figure 20.

The CS493xx family has integrated DTS tables, so

a ROM is required only for autoboot. The

CS493xx also has a static RAM interface. The

CDB49300-MEM external memory board is tai-

lored for the CDB49300. The CDB49300-MEM

schematic can be found in Figure

The CDB4923/300 has been designed to interface

to both the CRD4923-MEM and CDB49300-MEM

daughter boards. The card plugs directly on to J11

oriented such that the CS492x/CS493xx is not cov-

ered, as shown in Figure 1.

Please consult the memory map associated with the

revision of ROM installed in the memory card to

determine which code loads are available. The

memory map can be found in the ‘.fmt’ file found

on the included floppy.

4. CONTROL

Control of the CS492x/CS493xx can be accom-

plished in two ways. The CDB4923/300 is shipped

with a parallel computer cable which can be at-

tached to the parallel port (LPT1, LPT2, or LPT3)

of any computer which has a Windows or DOS

based operating system. The parallel port (J29) in-

terface circuitry is illustrated in Figure 6. The soft-

ware shipped with the CDB4923/300 is based on

command-line programs which must be executed

from a DOS prompt. The CDB4923/300 software

provides the means to reset the CS492x/CS493xx,

write control data to the DSP, read control data

from the DSP, and deliver compressed audio. A de-

tailed description of the software can be found in

Appendix F: Board Control Software.

Alternatively, the board can be put into a mode

which tri-states all connections between the PLD

and the DSP (full external mode), or a mode that

tri-states the control lines (external control mode)

of the CS492x/CS493xx while still driving the data

RD

J3

WR

J2

PSEL

J62

Host Interface Mode

0

1

1

Serial I

2

C (PSEL==SCDIO)

1

0

X

Serial SPI

1

1

0

8-bit Intel

1

1

1

8-bit Motorola

Table 1. CS492x/CS493xx Host Interface Mode Selection

Содержание CS492 Series

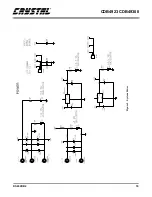

Страница 18: ...CDB4923 CDB49300 18 DS262DB2 9 APPENDIX A SCHEMATICS Figure 4 CS492x CS493xx ...

Страница 19: ...CDB4923 CDB49300 DS262DB2 19 Figure 5 System Power ...

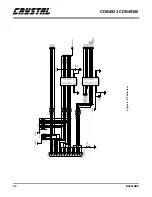

Страница 20: ...CDB4923 CDB49300 20 DS262DB2 Figure 6 PC Interface ...

Страница 21: ...CDB4923 CDB49300 DS262DB2 21 Figure 7 Control Logic ...

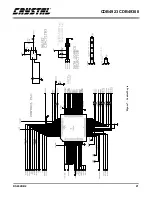

Страница 22: ...CDB4923 CDB49300 22 DS262DB2 Figure 8 Clocking ...

Страница 23: ...CDB4923 CDB49300 DS262DB2 23 Figure 9 Analog Input ...

Страница 24: ...CDB4923 CDB49300 24 DS262DB2 Figure 10 Digital Input ...

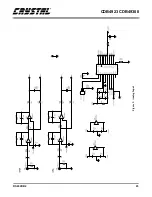

Страница 25: ...CDB4923 CDB49300 DS262DB2 25 Figure 11 D A Converters ...

Страница 26: ...CDB4923 CDB49300 26 DS262DB2 Figure 12 Analog Output ...

Страница 27: ...CDB4923 CDB49300 DS262DB2 27 Figure 13 Digital Output ...

Страница 28: ...CDB4923 CDB49300 28 DS262DB2 Figure 14 Top Layer ...

Страница 29: ...CDB4923 CDB49300 DS262DB2 29 Figure 15 Bottom Layer ...

Страница 30: ...CDB4923 CDB49300 30 DS262DB2 Figure 16 SSTOP ...

Страница 31: ...CDB4923 CDB49300 DS262DB2 31 Figure 17 ASYSTOP ...

Страница 32: ...CDB4923 CDB49300 32 DS262DB2 Figure 18 Layer 2 ...

Страница 33: ...CDB4923 CDB49300 DS262DB2 33 Figure 19 Layer 3 ...

Страница 49: ... Notes ...

Страница 50: ......