28

DS726PP2

CS4525

6.1.2

Power-Up and Power-Down

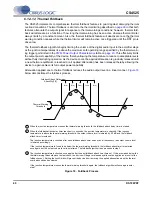

The CS4525 will remain in a completely powered-down state with the control port inaccessible until the

RST pin is brought high. Once RST is high, the control port will be accessible, but all other internal blocks

will remain powered-down until they are powered-up via the control port or until hardware mode is en-

tered.

When an external crystal is present on the XTI/XTO pins, software mode will be automatically entered

10 ms after the release of RST. If SYS_CLK is used as an input, software mode is entered by writing to

the control port within 10 ms after the release of RST. If the control port is not written within this time, the

device will begin to operate in hardware mode.

6.1.2.1

Recommended Power-Up Sequence

1.

Hold RST low until the power supplies and the input SYS_CLK (if used) are stable.

2.

Bring RST high.

The device will remain in a low-power state and the control port will be accessible. The device will

automatically enter software mode after 10 ms if an external crystal is present on the XTI/XTO pins,

at which time the output SYS_CLK signal will become active.

3.

If SYS_CLK is used as an input, initiate a control port write to set the PDnAll bit in register 5Fh within

10 ms following the release of RST.

This operation causes the device to enter software mode and places it in power-down mode.

4.

If the LVD pin is tied low and VD, VD_REG, and VA_REG are connected to 2.5 V, clear the SelectVD

bit in the Power Ctrl register to indicate the 2.5 V VD supply level. See

for de-

tails.

5.

If VP is connected to a supply voltage less than or equal to 14 V nominal, clear the SelectVP bit in the

Foldback Cfg register to indicate the VP supply level.

6.

The desired register settings can be loaded while keeping the PDnAll bit set. Typical initialization set-

tings include Input Configuration, Output Configuration, Master Volume, and Clock Frequency.

7.

Clear the PDnAll bit to initiate the power-up sequence.

6.1.2.2

Recommended Power-Down Sequence

1.

Set the MuteChA, MuteChB, and MuteSub bits in the Mute Control register to mute the audio output.

2.

Set the PDnAll bit to power-down the device.

3.

Bring RST low to bring the device’s power consumption to an absolute minimum.

4.

Remove power.

Referenced Control

Register Location

PDnAll .................................

“Power Down (PDnAll)” on page 89

SelectVD .............................

“Select VD Level (SelectVD)” on page 88

SelectVP .............................

“Select VP Level (SelectVP)” on page 74

MuteChX .............................

“Independent Channel A & B Mute (MuteChX)” on page 84

MuteSub..............................

“Sub Channel Mute (MuteSub)” on page 85

Input Configuration..............

“Input Configuration (Address 02h)” on page 71

Output Configuration ...........

“Output Configuration (Address 04h)” on page 73

Master Volume ....................

“Master Volume Control (Address 57h)” on page 82

Clock Frequency .................