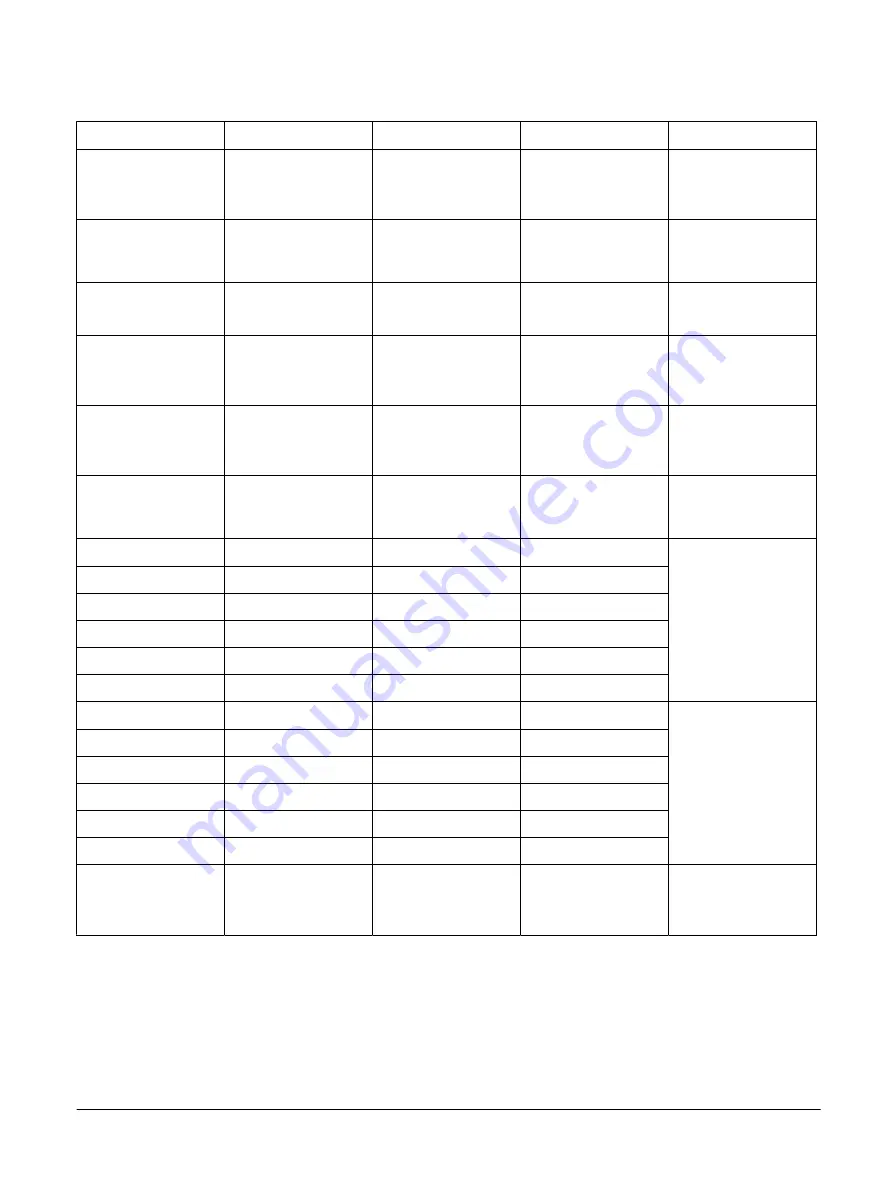

Table D5-1 PMU register summary in the AArch64 Execution state (continued)

Name

Type

Width

Reset

Description

PMCCFILTR_EL0

RW

32

UNK

Performance Monitors

Cycle Count Filter

Register

PMXEVCNTR_EL0

RW

32

UNK

Performance Monitors

Selected Event Count

Register

PMUSERENR_EL0

RW

32

UNK

Performance Monitors

User Enable Register

PMINTENSET_EL1

RW

32

UNK

Performance Monitors

Interrupt Enable Set

Register

PMINTENCLR_EL1

RW

32

UNK

Performance Monitors

Interrupt Enable Clear

Register

PMOVSSET_EL0

RW

32

UNK

Performance Monitors

Overflow Flag Status Set

Register

PMEVCNTR0_EL0

RW

32

UNK

Performance Monitors

Event Count Registers

PMEVCNTR1_EL0

RW

32

UNK

PMEVCNTR2_EL0

RW

32

UNK

PMEVCNTR3_EL0

RW

32

UNK

PMEVCNTR4_EL0

RW

32

UNK

PMEVCNTR5_EL0

RW

32

UNK

PMEVTYPER0_EL0

RW

32

UNK

Performance Monitors

Event Type Registers

PMEVTYPER1_EL0

RW

32

UNK

PMEVTYPER2_EL0

RW

32

UNK

PMEVTYPER3_EL0

RW

32

UNK

PMEVTYPER4_EL0

RW

32

UNK

PMEVTYPER5_EL0

RW

32

UNK

PMCCFILTR_EL0

RW

32

UNK

Performance Monitors

Cycle Count Filter

Register

Related references

C2.3 PMU events

on page C2-374

D5 AArch64 PMU registers

D5.1 AArch64 PMU register summary

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

D5-447

Non-Confidential

Содержание Cortex-A76 Core

Страница 4: ......

Страница 22: ......

Страница 23: ...Part A Functional description ...

Страница 24: ......

Страница 119: ...Part B Register descriptions ...

Страница 120: ......

Страница 363: ...Part C Debug descriptions ...

Страница 364: ......

Страница 401: ...Part D Debug registers ...

Страница 402: ......

Страница 589: ...Part E Appendices ...

Страница 590: ......