B4.12

AArch64 virtual GIC CPU interface register summary

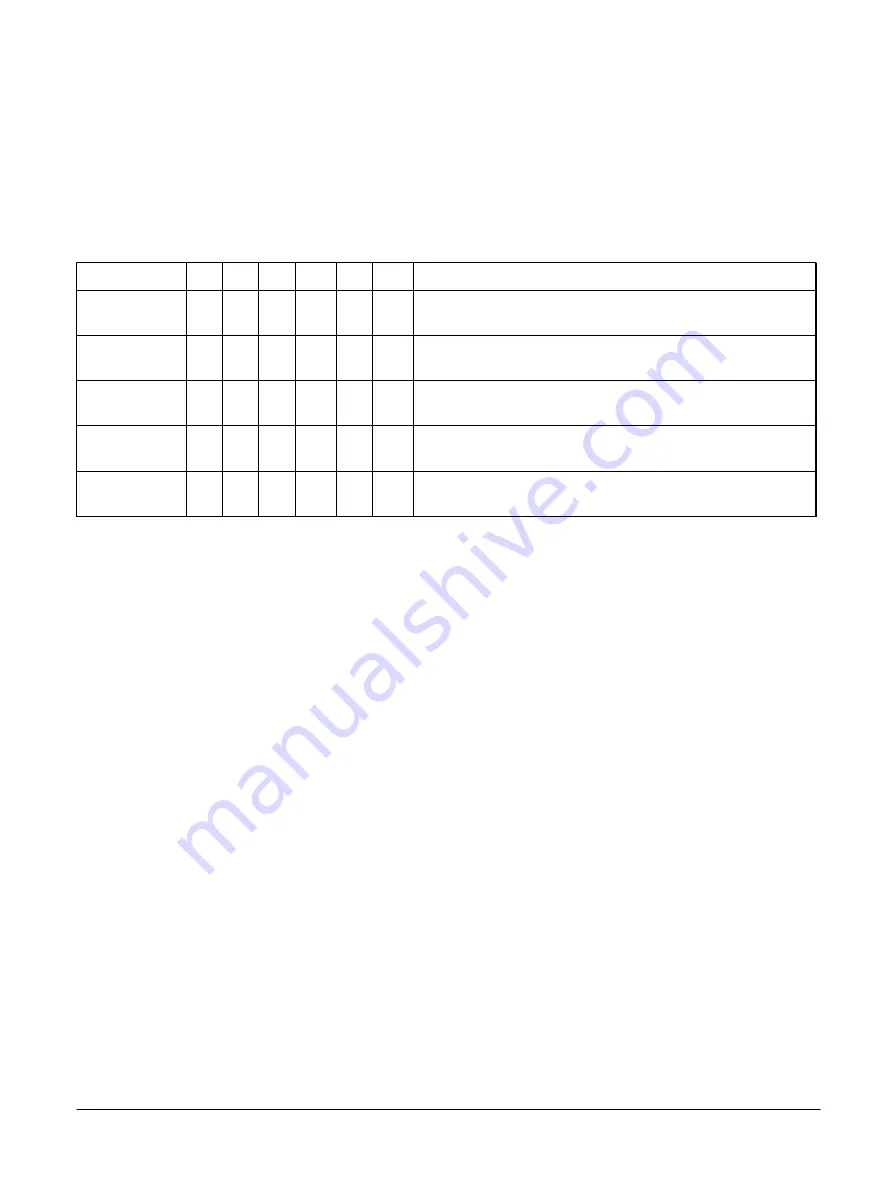

The following table describes the AArch64 virtual GIC CPU interface system registers that have

IMPLEMENTATION DEFINED

bits.

See the

Arm

®

Generic Interrupt Controller Architecture Specification

for more information and a

complete list of AArch64 virtual GIC CPU interface system registers.

Table B4-3 AArch64 virtual GIC CPU interface register summary

Name

Op0 Op1 CRn CRm Op2 Type Description

ICV_AP0R0_EL1 3

0

12

8

4

RW

B4.13 ICV_AP0R0_EL1, Interrupt Controller Virtual Active Priorities

Group 0 Register 0, EL1

ICV_AP1R0_EL1 3

0

12

9

0

RW

B4.14 ICV_AP1R0_EL1, Interrupt Controller Virtual Active Priorities

Group 1 Register 0, EL1

ICV_BRP0_EL1

3

0

12

8

3

RW

B4.15 ICV_BPR0_EL1, Interrupt Controller Virtual Binary Point

Register 0, EL1

ICV_BPR1_EL1

3

0

12

12

3

RW

B4.16 ICV_BPR1_EL1, Interrupt Controller Virtual Binary Point

Register 1, EL1

ICV_CTLR_EL1

3

0

12

12

4

RW

B4.17 ICV_CTLR_EL1, Interrupt Controller Virtual Control Register,

EL1

B4 GIC registers

B4.12 AArch64 virtual GIC CPU interface register summary

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

B4-328

Non-Confidential

Содержание Cortex-A76 Core

Страница 4: ......

Страница 22: ......

Страница 23: ...Part A Functional description ...

Страница 24: ......

Страница 119: ...Part B Register descriptions ...

Страница 120: ......

Страница 363: ...Part C Debug descriptions ...

Страница 364: ......

Страница 401: ...Part D Debug registers ...

Страница 402: ......

Страница 589: ...Part E Appendices ...

Страница 590: ......