10 A

NALOG

D

EVICES

,

I

NC

.

C

ONFIDENTIAL

DC9006A

AND

DC9004B

U

SER

G

UIDE

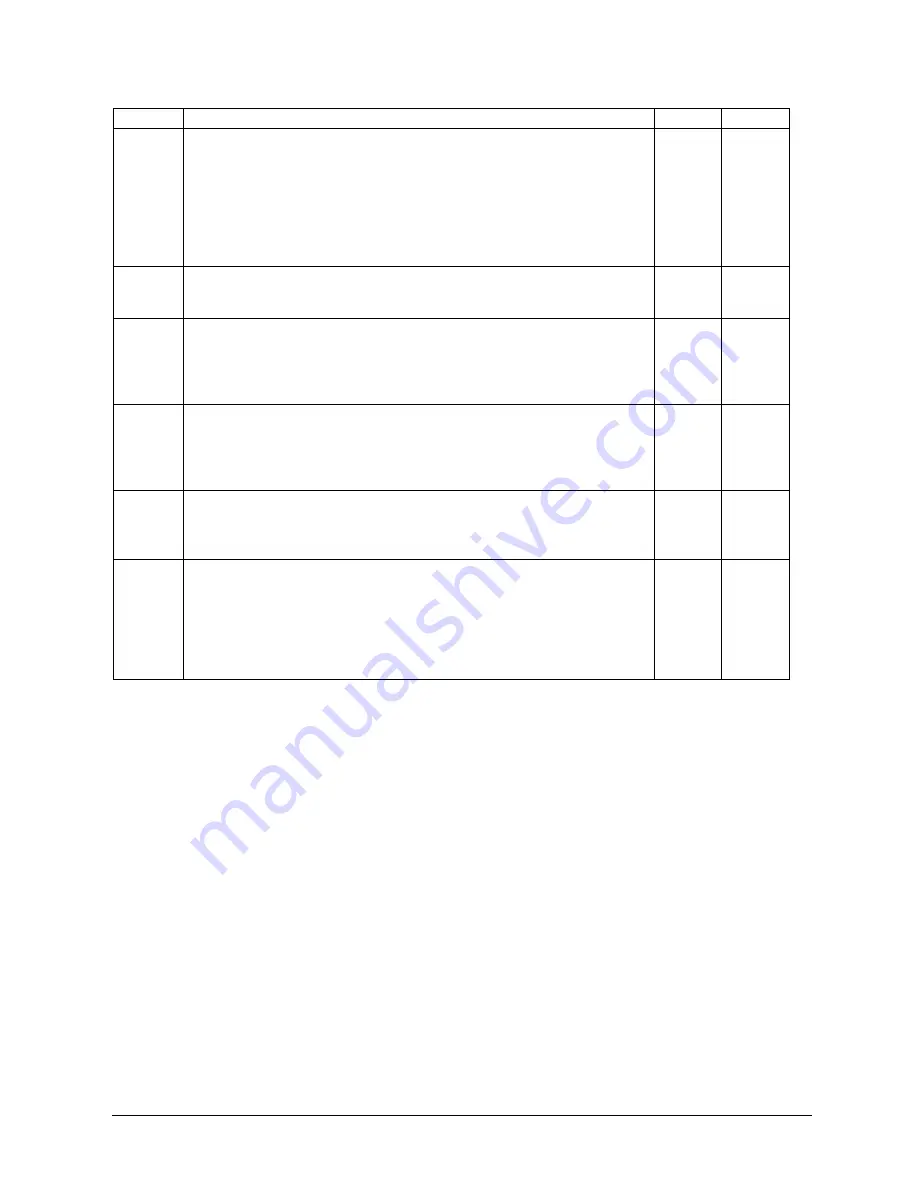

Jumper Description Default

Note

disconnects the JTAG lines from one of the USB serial interface and

should always be installed unless the USB JTAG interface is

supported in the development or evaluation tools;

"SPI OFF" to disconnect SPI lines, RESETn and FLASH_P_ENn;

"CLI OFF" to disconnect UARTC0 TX and RX; and,

"API OFF" to disconnect serial API signals.

OFF

OFF

OFF

JP5

Carries current to the Eterna Evaluation and Development Board.

JP5 should always be installed unless an ammeter is connected

across the P3 header.

ON

JP7

Enables the VCCA rail, the 3.6V isolated power supply to the Eterna

Evaluation and Development Board. JP7 should normally be

installed in the “ON” position (pin 1 & 2); the “OFF” position (pin 2

& 3) may be used to disable the VCCA rail and provide power from

an external source.

ON

(1)

JP8

Controls the isolated supplies of the Interface Card (V+ and the

derived VCCA and +5V rails). JP8 should normally be installed in

the “ON” position (pin 1 & 2); the “OFF” position (pin 2 & 3) may be

used to disable the on-board generation of the isolated V+ supply

and provide power from an external source set between 9V and 12V.

ON

(1)

JP9

Controls a power switch on the USB 5V supply. JP8 should

normally be installed in the “ON” position (pin 1 & 2); the “OFF”

position (pin 2 & 3) may be used to disconnect the Interface Card

from the USB 5V supply.

ON

(1)

JP10

Connects the Eterna Evaluation and Development Board battery to

logic that determines when power is to be switched from battery to

the isolated VCCA rail. JP10 jumper should normally be installed

for proper power switching operation. JP10 jumper may be

removed to prevent battery current flow in special situations such as

unpowered Interface Card connected to the Eterna Evaluation &

Development Board.

ON

(1) when no jumper is installed, the Interface Card defaults to the “ON” state

Interface Signal Disconnection

To perform accurate current measurements, it is recommended to disconnect the

Interface Card signals from the Eterna Evaluation & Development Board by

installing all JP1 jumpers.

Since so little power is required by the LTC5800 to operate, the Eterna Evaluation &

Development Board may gather enough power from current flowing through the

Interface Card signals and its ESD protection diodes.

External JTAG & Reset Pushbutton

The external JTAG connector (P1) allows the use of 3

rd

party development systems

with the Eterna Evaluation & Development Board. P1 is a 2x10 pin .100” header

compatible with JTAG/SWD emulators such as IAR or Segger J-Link.

The Interface Card features a momentary push button (PB1). PB1 only asserts the

JTAG and the Eterna Evaluation & Development Board reset signal (RESETn).