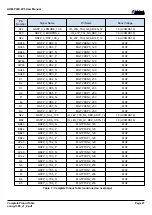

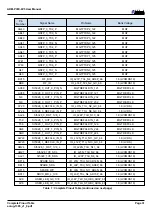

ADM-PCIE-9V5 User Manual

Appendix A: Complete Pinout Table

Pin

Number

Signal Name

Pin Name

Bank Voltage

BF12

AVR_B2U_1V8

IO_L2P_T0L_N2_66

1.8 (LVCMOS18)

BD12

AVR_HS_B2U_1V8

IO_L1P_T0L_N0_DBC_66

1.8 (LVCMOS18)

BC8

AVR_HS_CLK_1V8

IO_L12N_T1U_N11_GC_66

1.8 (LVCMOS18)

BE12

AVR_HS_U2B_1V8

IO_L1N_T0L_N1_DBC_66

1.8 (LVCMOS18)

BC9

AVR_MON_CLK_1V8

IO_L12P_T1U_N10_GC_66

1.8 (LVCMOS18)

BF11

AVR_U2B_1V8

IO_L2N_T0L_N3_66

1.8 (LVCMOS18)

AR8

CAPI_CLK_1_PIN_N

MGTREFCLK0N_224

MGT REFCLK

AR9

CAPI_CLK_1_PIN_P

MGTREFCLK0P_224

MGT REFCLK

AL8

CAPI_CLK_2_PIN_N

MGTREFCLK0N_225

MGT REFCLK

AL9

CAPI_CLK_2_PIN_P

MGTREFCLK0P_225

MGT REFCLK

BE24

CAPI_I2C_SCL_1V8

IO_L1P_T0L_N0_DBC_64

1.8 (LVCMOS18)

BF24

CAPI_I2C_SDA_1V8

IO_L1N_T0L_N1_DBC_64

1.8 (LVCMOS18)

BC23

CAPI_INT/RESET_1V8

IO_L2P_T0L_N2_64

1.8 (LVCMOS18)

BB1

CAPI_RX0_N

MGTYRXN0_224

MGT

BB2

CAPI_RX0_P

MGTYRXP0_224

MGT

AY1

CAPI_RX1_N

MGTYRXN1_224

MGT

AY2

CAPI_RX1_P

MGTYRXP1_224

MGT

AV1

CAPI_RX2_N

MGTYRXN2_224

MGT

AV2

CAPI_RX2_P

MGTYRXP2_224

MGT

AT1

CAPI_RX3_N

MGTYRXN3_224

MGT

AT2

CAPI_RX3_P

MGTYRXP3_224

MGT

AP1

CAPI_RX4_N

MGTYRXN0_225

MGT

AP2

CAPI_RX4_P

MGTYRXP0_225

MGT

AM1

CAPI_RX5_N

MGTYRXN1_225

MGT

AM2

CAPI_RX5_P

MGTYRXP1_225

MGT

AK1

CAPI_RX6_N

MGTYRXN2_225

MGT

AK2

CAPI_RX6_P

MGTYRXP2_225

MGT

AJ3

CAPI_RX7_N

MGTYRXN3_225

MGT

AJ4

CAPI_RX7_P

MGTYRXP3_225

MGT

BE4

CAPI_TX0_N

MGTYTXN0_224

MGT

BE5

CAPI_TX0_P

MGTYTXP0_224

MGT

BC4

CAPI_TX1_N

MGTYTXN1_224

MGT

BC5

CAPI_TX1_P

MGTYTXP1_224

MGT

Table 7 : Complete Pinout Table (continued on next page)

Page 23

Complete Pinout Table

ad-ug-1385_v1_0.pdf