ADM-PCIE-9V5 User Manual

3.2.1 Si5328

If jitter attenuation is required please see the reference documentation for the Si5328.

https://www.silabs.com/Support%20Documents/TechnicalDocs/Si5328.pdf

The circuit connections mirror the Xilinx VCU110 and VCU108 Development Kits. Please refer to the Xilinx

documentation for information.

The CLKIN2 input of the SI5328, provided by the SI5338, is only available in rev2 PCBs and onward (Serial

number greater than 109).

3.2.2 PCIe Reference Clocks

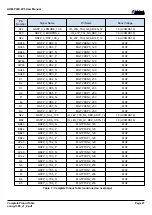

The 8 MGT lanes connected to the PCIe card edge use MGT tiles 226 through 227 and use the system 100 MHz

clock (net name PCIE_REFCLK).

Alternatively, a clean, onboard 100MHz clock is available as well (net name PCIE_LCL_REFCLK).

3.2.3 Fabric Clock

The design offers a fabric clock (net name FABRIC_CLK_*) which defaults to 300 MHz. This clock is intended to

be used for IDELAY elements in FPGA designs. The fabric clock is connected to a Global Clock (GC) pin.

DIFF_TERM_ADV = TERM_100 is required for LVDS termination

3.2.4 Programming Clock (EMCCLK)

A 100MHz clock (net name EMCCLK_B) is fed into the EMCCLK pin to drive the SPI flash device during

configuration of the FPGA. Note that this is not a global clock capable IO pin.

3.2.5 QSFP-DD

The QSFP-DD clocks have a default 156.25MHz reference clock. Note that this clock frequency can be changed

to any arbitrary clock frequency up to 312MHz by re-programing the Si5338 reprogrammable clock oscillator.

See details on avr2util in the section:

See net names MGT_PROGCLK_* for pin locations.

The QSFP-DD cages are also located such that they can be clocked from the Si5328 jitter attenuators.

See net names SI5328_OUT_* for pin locations.

3.2.6 Ultraport SlimSAS (OpenCAPI)

The Ultraport SlimSAS connector is located in MGT tile 224 and 225.

For OpenCAPI an external 156.25MHz clock is provided over the cable. See net names CAPI_CLK_* for cable

clock pin locations.

Another alternative clock source for this interface is the PCIE_LCL_REFCLK clock synthesizer at 100MHz.

For jitter sensitive applications, this interface can be clocked from the Si5328 jitter attenuator. See net names

SI5328_OUT_* for pin locations.

Page 12

Functional Description

ad-ug-1385_v1_0.pdf