4

5. Squelch Circuit

The signal except for the noise component in AF signal of IC5 is cut by the

active filter inside IC. The noise component is amplified and rectified, then con-

verted to the DC voltage to output from pin13 of IC5. The voltage is led to pin 2

of CPU and compared with the setting voltage. The squelch will open if the

input voltage is lower than the setting voltage.

2) Transmitter System

1. Modulator Circuit

The audio signal is converted to an electric signal in either the internal or exter-

nal microphone, and input to the microphone amplifier (IC7). IC7 consists of

two operational amplifiers; one amplifier (pins 5, 6, and 7) is composed of pre-

emphasis and IDC circuits and the other (pins 1, 2, and 3) is composed of a

splatter filter. The maximum frequency deviation is obtained by VR202 and

input to the cathode of the varicap of the VCO, to change the electric capacity

in the oscillation circuit. This produces the frequency modulation.

2. Power Amplifier Circuit

The transmitted signal is oscillated by the VCO, amplified by the pre-drive

amplifier (Q4) and drive amplifier (Q3), and input to the final amplifier (Q2). The

signal is then amplified by the final amplifier (Q2) and led to the antenna switch

(D1) and low-pass filter (L5, L4, L3, L2, C16, C15, C14 and C13), where un-

wanted high harmonic waves are reduced as needed, and the resulting signal

is supplied to the antenna.

3. APC Circuit

Part of the transmission power from the low-pass filter is detected by D6, con-

verted to DC, and then amplified by a differential amplifier. The output voltage

controls the bias voltage from the source of Q2 and Q3 to maintain the trans-

mission power constant.

3) PLL Synthesizer Circuit

1. PLL

The dividing ratio is obtained by sending data from the CPU (IC9) to pin 2 and

sending clock pulses to pin 3 of the PLL IC (IC1). The oscillated signal from the

VCO is amplified by the buffer (Q5) and input to pin 6 of IC1. Each program-

mable divider in IC1 divides the frequency of the input signal by N according to

the frequency data, to generate a comparison frequency of 5 or 6.25kHz.

2. Reference Frequency Circuit

The reference frequency appropriate for the channel steps is obtained by divid-

ing the 21.25MHz reference oscillation (X1) by 4250 or 3400, according to the

data from the CPU (IC9). When the resulting frequency is 5kHz, channel steps

of 5, 10, 15, 20, 25, 30, and 50kHz are used. When it is 6.25kHz, the 12.5kHz

channel step is used.

Содержание DJ-195

Страница 2: ......

Страница 11: ...10 3 M5222FP 600C XA0385 Electronic Volume ...

Страница 12: ...11 4 TK14521MTL XA0515 IF System ...

Страница 14: ...13 8 S 81250SG QD T1 XA0619 Top View 9 S 80845ALMP EA9 T2 XA0620 Voltage Regulator ...

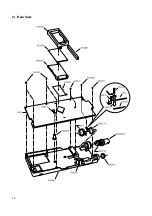

Страница 16: ...15 EXPLODED VIEW 1 Front View www ALIMCO ru ...

Страница 17: ...16 2 Rear View ...

Страница 28: ......

Страница 29: ...27 PC BOARD VIEW MAIN SIDE A MAIN Side B ...

Страница 30: ...28 SCHEMATIC DIAGRAM ...

Страница 31: ...29 BLOCK DIAGRAM www ALIMCO ru ...

Страница 32: ......

Страница 33: ......