30

•

Operation Theorem

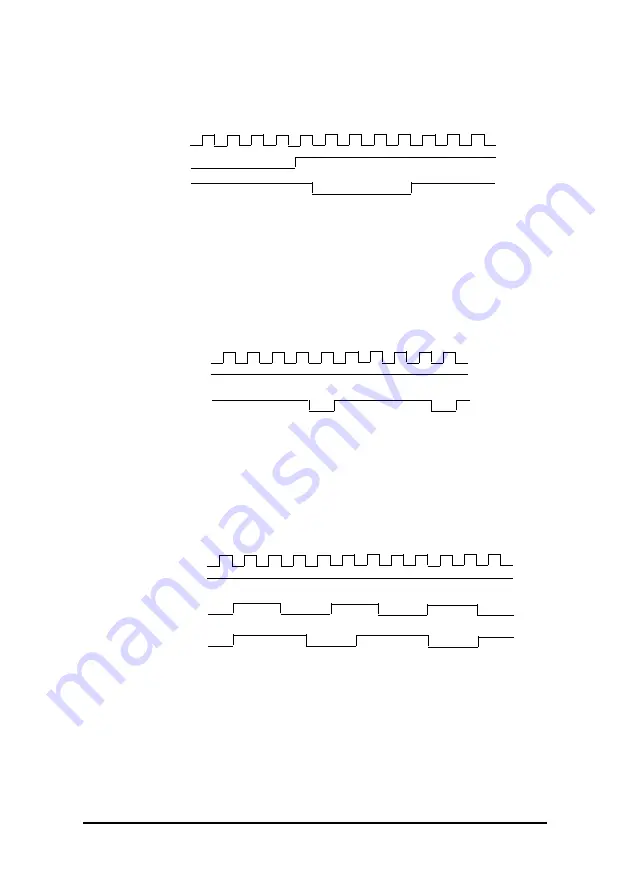

The following diagram shows the timing diagram.

Clock

Gate

Output

4 3 2 1 0

(n = 4)

Mode 2 : Rate Generator

In this mode, the output goes low for one period of the clock input. The

value fill in the counter indicates the period from one output pulse to the

next.

The following diagram shows the timing diagram.

Clock

Gate

Output

4 3 2 1 0 (4) 3 2 1 0 (4)

(n = 4)

Mode 3 : Square Wave Mode

In this mode, the output stays high for one half of the

count

clock pulses

and stays low for the other half.

The following diagram shows the timing diagram.

Clock

Gate

Output (n = 4)

4 2 4 2 4 2 4 2 4 2 4 2

Output (n = 5)

5 4 2 5 2 5 4 2 5 2 5 4

Mode 4 : Software Triggered Strobe

In this mode, the output is initially high, and the counter begins to count

down while the gate input is high. On terminal count, the output goes

low for one clock pulse, and goes high again.

Содержание USBDAQ-9100MS

Страница 1: ...USBDAQ 9100MS Universal Serial Bus Multi Functions Data Acquisition Module User s Guide Recycled Paper...

Страница 2: ......

Страница 6: ...ii Table of Contents Warranty Policy 32...

Страница 26: ...20 Signal Connections DIN 68S View...