SERIES AP470 ACROPACK

USER

’S MANUAL

Acromag, Inc. Tel: 248-295-0310

- 6 -

http://www.acromag.com

- 6 -

www.acromag.com

1.3 AcroPack Information – All Models

AcroPack IO modules are based on the PCI Express Mini Card

Electromechanical specification and are 70mm in length with an additional

100 pin field I/O connector.

The AcroPack is 19.05mm longer than the full length mini PCIe card at

50.95mm. It has the same mPCIe board width of 30mm and uses the same

mPCIe standard board hold down standoff and screw keep out areas.

The AP470 module provides 48 channels of general-purpose digital inputs

and outputs. Inputs and outputs of this module are CMOS and TTL

compatible. Each of the I/O lines can be used as either an input, an output,

or an output with read-back capability. Each I/O line has built-in event sense

circuitry with programmable polarity and interrupt support. The inputs may

also operate as independent event sense inputs (without interrupts).

Outputs are open drain and may sink up to 15mA each. A 4.7K pull-up is

provided for each drain. Inputs include hysteresis and programmable

debounce. Interrupt, event, and debounce functionality applies to all 48

channels of this model. The AP470 utilizes state of the art Surface-Mounted

Technology (SMT) to achieve its wide functionality and is an ideal choice for

a wide range of industrial I/O applications that require a high-density, highly

reliable, high-performance interface at a low cost.

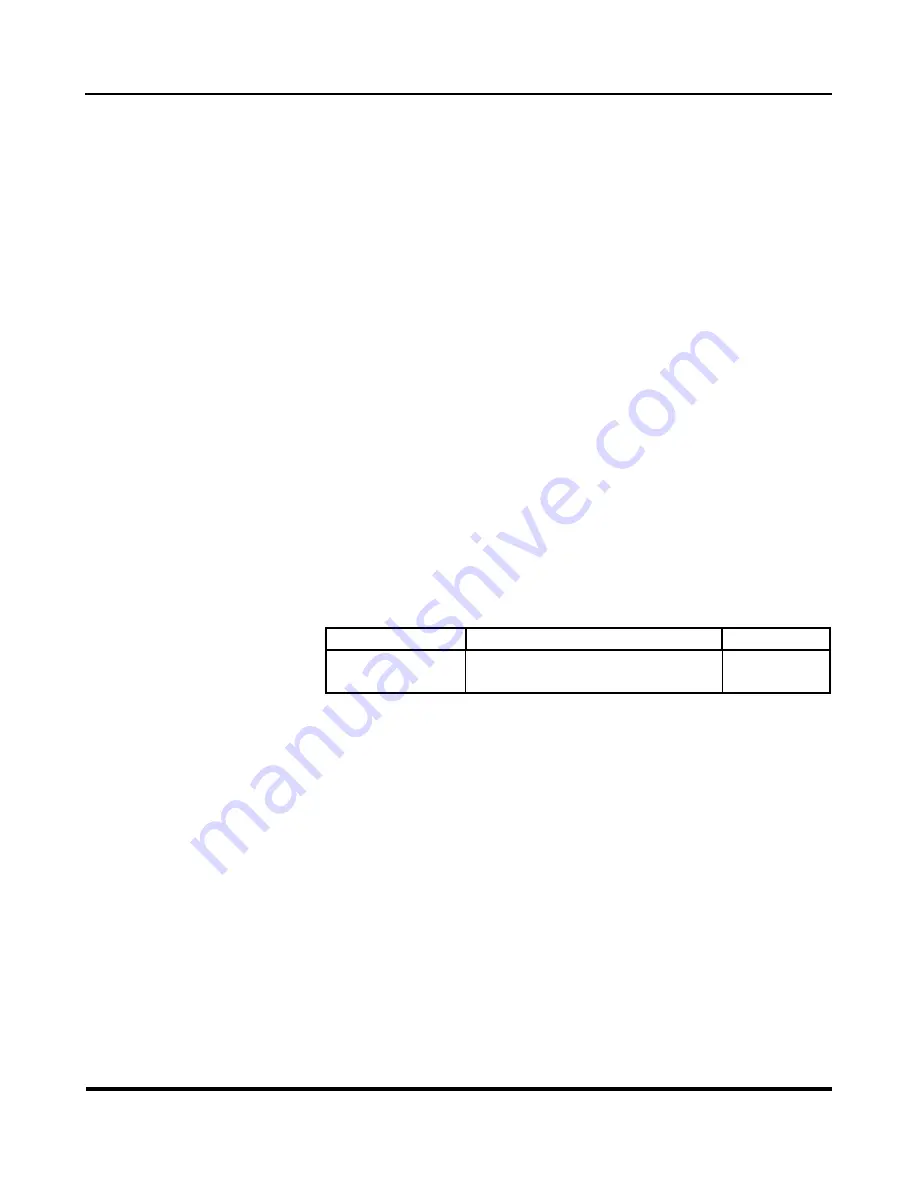

1.3.1 Ordering Information

The AcroPack ordering options are given in the following table.

Model Number

Description

Temp Range

AP470E-LF

1

48-Channel Digital I/O

-40

o

C to 85

o

C

Note 1: Applications requiring operating temperatures of 70°C to

85°C will require purchase of AcroPack Heatsink Accessory AP-CC-

01 with a minimum airflow of 200LFM. For temperatures below

70°C the module will require a minimum airflow of 200LFM.

AP-CC-01 AcroPack Conduction Cool Kit (See Appendix B for

installation instructions)

1.3.2 Key Features

High Channel Count - Provides programmable monitor and control

of 48 I/O points.

Programmable Polarity Event Interrupts (all 48 channels) -

Interrupts are software programmable for positive (low-to-high) or

negative (high-to-low) input level transitions on all 48 channels.

Using two channels per input signal, change-of-state transitions may

also be configured for up to 24 inputs.