UM008 FMC204 User Manual

r1.14

UM008

- 16 -

FMC204

CLOCK

TRIGGER/SYNC

FMC204

CLOCK

TRIGGER/SYNC

FMC204

CLOCK

TRIGGER/SYNC

Clock generation

Fs 50%

Fs/4 25%

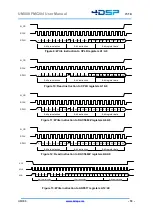

Figure 7: Synchronizing multiple cards

5

Controlling the FMC204

5.1 Architecture

The FMC must be controlled from the carrier hardware through a single SPI communication

bus. The SPI communication bus is connected to a CPLD which has the following tasks:

Distribute SPI access from the carrier hardware along the local devices:

-

2x DAC5682Z (D/A converters)

-

1x AD9517 (Clock Tree)

Select clock source based on a SPI command from the carrier hardware

(CLKSRC_SEL).

Select sync source based on a SPI command from the carrier hardware

(SYNCSRC_SEL).

Generate SPI reset for AD9517 (CLK_N_RESET) and both DAC5682Z

(DAC_N_RESET)

Control the direction of the front I/O transceivers (FRONT_IO_DIR).

Control the FAN header power (FAN_N_EN).

Collect local status signals and store them in a register which can be accessed from

the carrier hardware.

Drive a LED according to the level of the status signals.