Summary of Contents for 17MB11

Page 1: ...50 PLASMA TV 17MB11 SERVICE MANUAL...

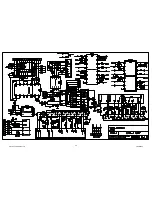

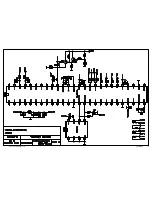

Page 50: ...47 Plasma TV Service Manual 25 08 2005 15 CIRCUIT DIAGRAMS...

Page 51: ...48 Plasma TV Service Manual 25 08 2005...

Page 52: ...49 Plasma TV Service Manual 25 08 2005...

Page 53: ...50 Plasma TV Service Manual 25 08 2005...

Page 54: ...51 Plasma TV Service Manual 25 08 2005...

Page 55: ...52 Plasma TV Service Manual 25 08 2005...

Page 56: ...53 Plasma TV Service Manual 25 08 2005...

Page 57: ...54 Plasma TV Service Manual 25 08 2005...