LISA-U1 series - System Integration Manual

3G.G2-HW-10002-3

Preliminary

System description

Page 43 of 125

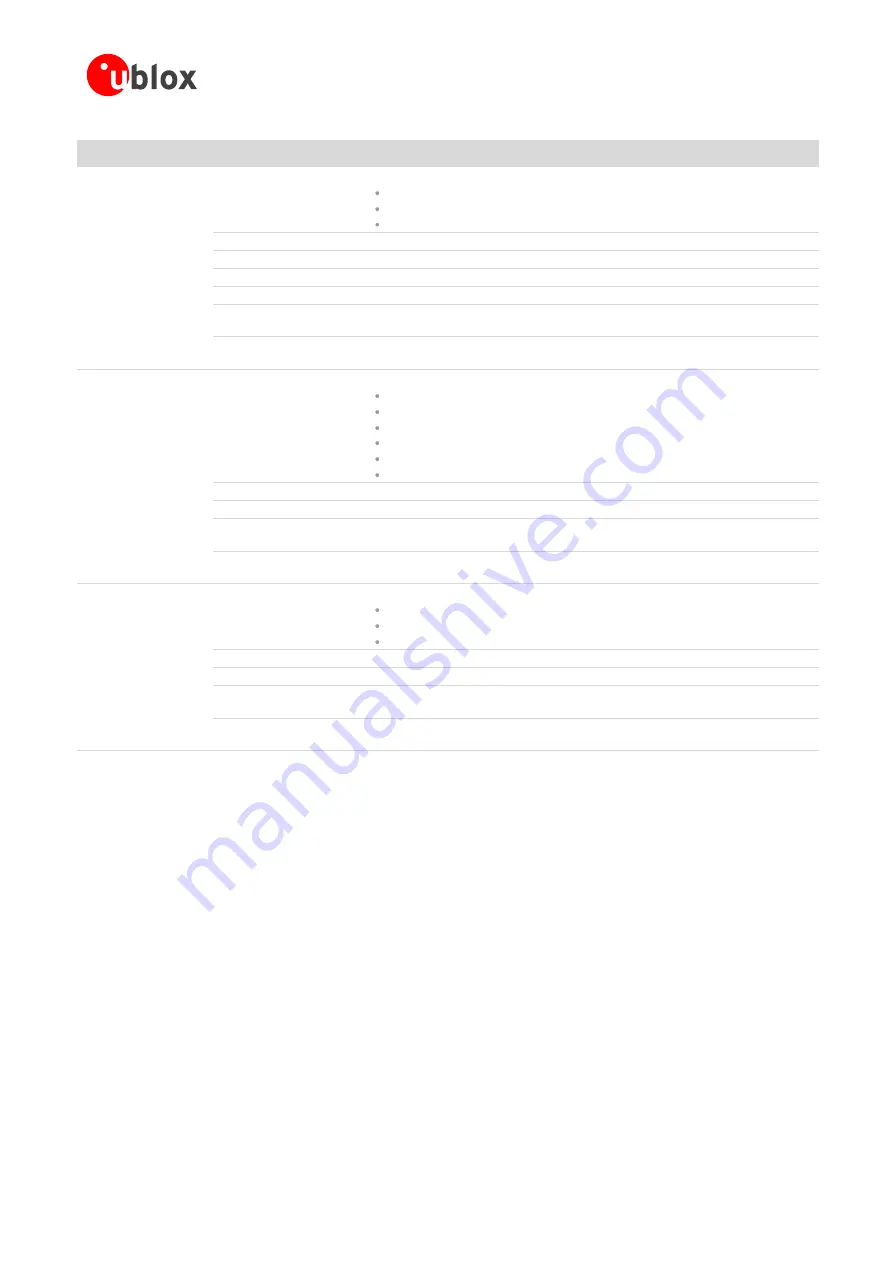

Interface

AT Settings

Comments

UART interface

Enabled

Multiplexing mode can be enabled by AT+CMUX command providing following channels:

Channel 0: control channel

Channel 1 – 5: AT commands /data connection

Channel 6: GPS tunneling

AT+IPR=115200

Baud rate: 115200 b/s

AT+ICF=0,0

Frame format: 8 bits, no parity, 1 stop bit

AT&K3

HW flow control enabled

AT&S1

DSR line set ON in data mode and set OFF in command mode

AT&D1

Upon an ON-to-OFF transition of DTR, the DCE enters online command state and issues

an OK result code

AT&C1

Circuit 109 changes in accordance with the Carrier detect status; ON if the Carrier is

detected, OFF otherwise

USB interface

Enabled

6 CDCs are available, configured as described in the following list:

USB1: AT commands / data connection

USB2: AT commands / data connection

USB3: AT commands / data connection

USB4: GPS tunneling dedicated port

USB5: 2G and BB trace dedicated port

USB6: 3G trace dedicated port

AT&K3

HW flow control enabled

AT&S1

DSR line set ON in data mode and set OFF in command mode

AT&D1

Upon an ON-to-OFF transition of DTR, the DCE enters online command state and issues

an OK result code

AT&C1

Circuit 109 changes in accordance with the Carrier detect status; ON if the Carrier is

detected, OFF otherwise

SPI interface

Enabled

Multiplexing mode can be enabled by AT+CMUX command providing following channels:

Channel 0: control channel

Channel 1 – 5: AT commands /data connection

Channel 6: GPS tunneling

AT&K3

HW flow control enabled

AT&S1

DSR line set ON in data mode and set OFF in command mode

AT&D1

Upon an ON-to-OFF transition of DTR, the DCE enters online command state and issues

an OK result code

AT&C1

Circuit 109 changes in accordance with the Carrier detect status; ON if the Carrier is

detected, OFF otherwise

Table 18: Default serial interfaces configuration

1.9.2

Asynchronous serial interface (UART)

The UART interface is a 9-wire unbalanced asynchronous serial interface that provides AT commands interface,

PSD and CSD data communication, firmware upgrade.

UART interface provides RS-232 functionality conforming to the ITU-T V.24 Recommendation (more details

available in

ITU Recommendation

[3]), with CMOS compatible signal levels: 0 V for low data bit or ON state, and

1.8 V for high data bit or OFF state. Two different external voltage translators (e.g. Maxim MAX3237E and Texas

Instruments SN74AVC8T245PW) could be used to provide full RS-232 (9 lines) compatible signal levels. The

Texas Instruments chip provides the translation from 1.8 V to 3.3 V, while the Maxim chip provides the necessary

RS-232 compatible signal towards the external connector. If a UART interface with only 5 lines is needed, the

Maxim 13234E voltage level translator can be used. This chip translates the voltage levels from 1.8 V (module

side) to the RS-232 standard. For detailed electrical characteristics refer to

LISA-U1 series

Data Sheet

The LISA-U1 series modules are designed to operate as an HSPA wireless modem, which represents the data

circuit-terminating equipment (DCE) as described by the

ITU-T V.24 Recommendation

[3]. A customer application

processor connected to the module through the UART interface represents the data terminal equipment (DTE).