1

1

2

2

3

3

4

4

D

D

C

C

B

B

A

A

Date:

Page

8

of

21

Number:

Title:

TEI0006

01

Rev.

A4

Copyright:

Trenz Electronic GmbH

C10GX_2A.SchDoc

Filename:

2018-07-27

220-5I

TEI0006

IO/DATA0/LVDS2A_1n/X4_DQ24/X8_DQ12/X16_DQ6/X32_DQ3

IO/DATA1/LVDS2A_1p/X4_DQ24/X8_DQ12/X16_DQ6/X32_DQ3

IO/DATA2/LVDS2A_2n/X4_DQSn24/X8_DQ12/X16_DQ6/X32_DQ3

IO/DATA3/LVDS2A_2p/X4_DQS24/X8_DQ12/X16_DQ6/X32_DQ3

IO/DATA4/LVDS2A_3n/X4_DQ24/X8_DQ12/X16_DQ6/X32_DQ3

IO/DATA5/LVDS2A_3p/X4_DQ24/X8_DQ12/X16_DQ6/X32_DQ3

IO/DATA6/LVDS2A_4n/X4_DQSn25/X8_DQSn12/CQn12/X16_DQ6/X32_DQ3

IO/DATA7/LVDS2A_4p/X4_DQS25/X8_DQS12/CQ12/X16_DQ6/X32_DQ3

IO/DATA8/LVDS2A_5n/X4_DQ25/X8_DQ12/X16_DQ6/X32_DQ3

IO/DATA9/LVDS2A_5p/X4_DQ25/X8_DQ12/X16_DQ6/X32_DQ3

IO/DATA10/LVDS2A_6n/X4_DQ25/X8_DQ12/X16_DQSn6/CQn6/X32_DQ3

IO/DATA11/LVDS2A_6p/X4_DQ25/X8_DQ12/X16_DQS6/CQ6/X32_DQ3

IO/DATA12/LVDS2A_7n/X4_DQ26/X8_DQ13/X16_DQ6/X32_DQ3

IO/DATA13/LVDS2A_7p/X4_DQ26/X8_DQ13/X16_DQ6/X32_DQ3

IO/DATA14/LVDS2A_8n/X4_DQSn26/X8_DQ13/X16_DQ6/X32_DQ3

IO/DATA15/LVDS2A_8p/X4_DQS26/X8_DQ13/X16_DQ6/X32_DQ3

IO/DATA16/LVDS2A_9n/X4_DQ26/X8_DQ13/X16_DQ6/X32_DQ3

IO/DATA17/LVDS2A_9p/X4_DQ26/X8_DQ13/X16_DQ6/X32_DQ3

IO/PLL_2A_CLKOUT1n/DATA18/LVDS2A_10n/X4_DQSn27/X8_DQSn13/CQn13/X16_DQ6/X32_DQ3

IO/nCEO/LVDS2A_11n/X4_DQ27/X8_DQ13/X16_DQ6/X32_DQ3

IO/CLK_2A_1n/DATA20/LVDS2A_12n/X4_DQ27/X8_DQ13/X16_DQ6/X32_DQ3

IO/CLK_2A_1p/DATA21/LVDS2A_12p/X4_DQ27/X8_DQ13/X16_DQ6/X32_DQ3

IO/CLK_2A_0n/DATA22/LVDS2A_13n/X4_DQ28/X8_DQ14/X16_DQ7/X32_DQ3

IO/CLK_2A_0p/DATA23/LVDS2A_13p/X4_DQ28/X8_DQ14/X16_DQ7/X32_DQ3

IO/DATA24/LVDS2A_14n/X4_DQSn28/X8_DQ14/X16_DQ7/X32_DQSn3/CQn3

IO/DATA25/LVDS2A_14p/X4_DQS28/X8_DQ14/X16_DQ7/X32_DQS3/CQ3

IO/PLL_2A_CLKOUT0n/DATA26/LVDS2A_15n/X4_DQ28/X8_DQ14/X16_DQ7/X32_DQ3

IO/PLL_2A_CLKOUT0p,PLL_2A_CLKOUT0,PLL_2A_FB0/DATA27/LVDS2A_15p/X4_DQ28/X8_DQ14/X16_DQ7/X32_DQ3

IO/DATA28/LVDS2A_16n/X4_DQSn29/X8_DQSn14/CQn14/X16_DQ7/X32_DQ3

IO/DATA29/LVDS2A_16p/X4_DQS29/X8_DQS14/CQ14/X16_DQ7/X32_DQ3

IO/DATA30/LVDS2A_17n/X4_DQ29/X8_DQ14/X16_DQ7/X32_DQ3

IO/DATA31/LVDS2A_17p/X4_DQ29/X8_DQ14/X16_DQ7/X32_DQ3

IO/CLKUSR/LVDS2A_18n/X4_DQ29/X8_DQ14/X16_DQSn7/CQn7/X32_DQ3

IO/nPERSTL0/LVDS2A_19p/X4_DQ30/X8_DQ15/X16_DQ7/X32_DQ3

IO/CvP_CONFDONE/LVDS2A_22n/X4_DQSn31/X8_DQSn15/CQn15/X16_DQ7/X32_DQ3

IO/INIT_DONE/LVDS2A_23n/X4_DQ31/X8_DQ15/X16_DQ7/X32_DQ3

IO/DEV_OE/LVDS2A_23p/X4_DQ31/X8_DQ15/X16_DQ7/X32_DQ3

IO/CRC_ERROR/LVDS2A_24n/X4_DQ31/X8_DQ15/X16_DQ7/X32_DQ3

IO/DEV_CLRn/LVDS2A_24p/X4_DQ31/X8_DQ15/X16_DQ7/X32_DQ3

IO/LVDS2A_18p/X4_DQ29/X8_DQ14/X16_DQS7/CQ7/X32_DQ3

IO/LVDS2A_19n/X4_DQ30/X8_DQ15/X16_DQ7/X32_DQ3

IO/LVDS2A_20n/X4_DQSn30/X8_DQ15/X16_DQ7/X32_DQ3

IO/LVDS2A_20p/X4_DQS30/X8_DQ15/X16_DQ7/X32_DQ3

IO/LVDS2A_21n/X4_DQ30/X8_DQ15/X16_DQ7/X32_DQ3

IO/LVDS2A_21p/X4_DQ30/X8_DQ15/X16_DQ7/X32_DQ3

IO/LVDS2A_22p/X4_DQS31/X8_DQS15/CQ15/X16_DQ7/X32_DQ3

IO/RZQ_2A/LVDS2A_11p/X4_DQ27/X8_DQ13/X16_DQ6/X32_DQ3

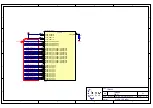

U23F

10CX220YF780I5G

ETH1_RXCK

ETH1_RXD0

ETH1_RXD1

ETH1_RXD2

ETH1_RXD3

ETH1_RXDV

ETH1_CLK125

ETH1_MDC

ETH1_MDIO

ETH1_TXD0

ETH1_TXD1

ETH1_TXD2

ETH1_TXD3

ETH1_TXEN

ETH1_RST

ETH1_GTXCK

QSPI_DATA0

QSPI_DATA2

QSPI_DATA3

QSPI_CS

QSPI_DATA1

QSPI_CLK

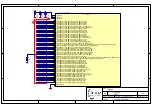

1.8VIO

6.3V

X5R

C159

47nF

6.3V

X5R

C158

470nF

6.3V

X5R

C155

4.7µF

GND

GND

GND

DEV_CLRN

GND

i

ETH_PHY

QSPI_RST

CLKUSR

INIT_DONE

M10_IO1

PERST

i

2A

CLK0_P

CLK0_N

1%

R107

100R

1%

R14 1K

GND

1%

R108 4K7

1%

R109 4K7

1%

R110 4K7

1.8VIO

M10_IO2

M10_IO3

M10_IO4

ETH1_TXCLK

ETH1_TXER

ETH1_TXD4

ETH1_TXD5

ETH1_TXD6

ETH1_TXD7

ETH1_RXD4

ETH1_RXD5

ETH1_RXD6

ETH1_RXD7

ETH1_RXER

ETH1_COL

ETH1_CRS

DATA0

CLK_GMII

ETH_CLKIN

50V

NP0

C215

50V

NP0

C216

68pF

GND