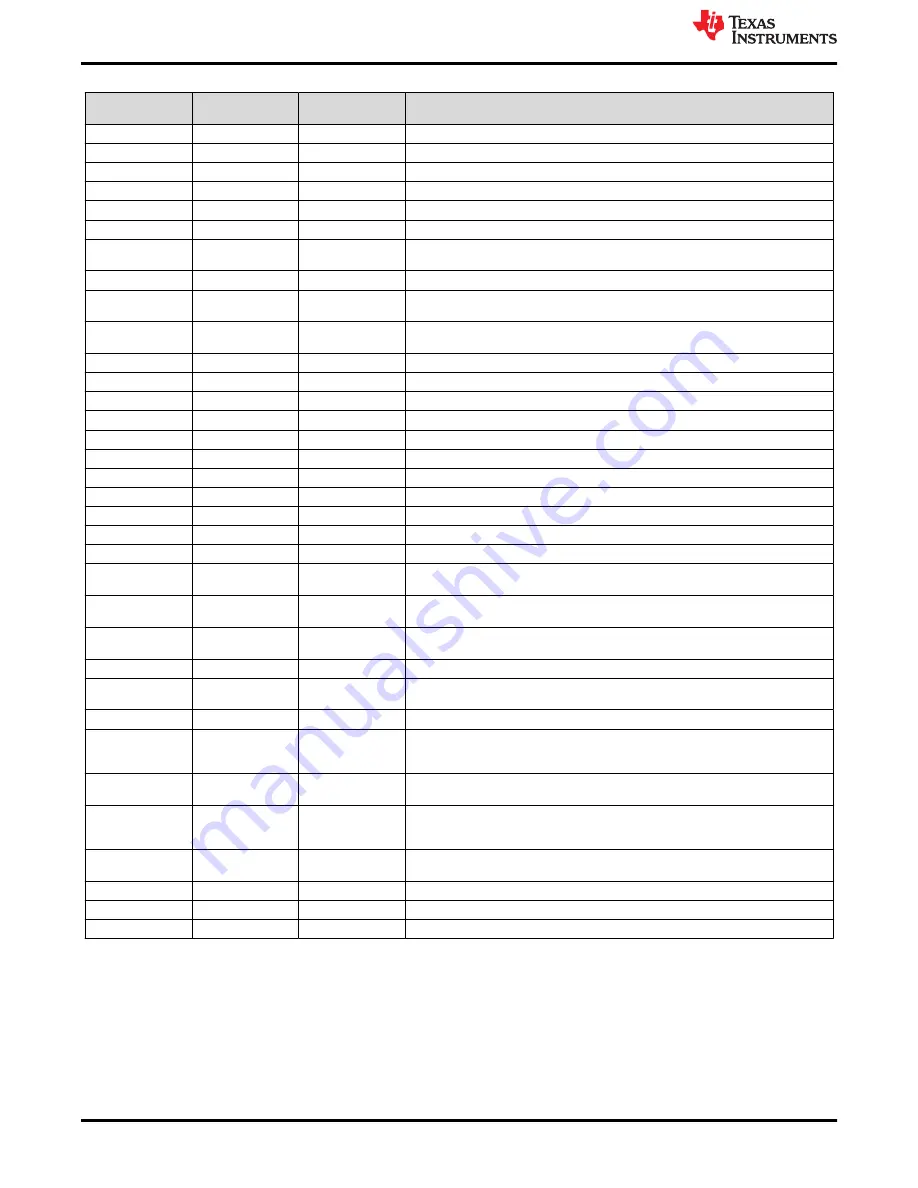

Table 3-2. Test Points

REFERENCE

DESIGNATOR

NAME

RELATED IC

FUNCTION

TP1

VIN_U1

U1

VIN test point. Use this for efficiency measurements.

TP2

VOUT_U1

U1

VOUT test point. Use this for efficiency, output regulation, and bode plot measurements.

TP3

SW_U1

U1

SW node solder mask opening

TP4

PGND_U1

U1

PGND test point

TP5

PGND_EFF_U1

U1

PGND test point. Use this for efficiency measurements.

TP6

PGOOD_U1

U1

PGOOD test point

TP7

EN_U1

U1

EN test point. If applying an external voltage, it must be kept below the absolute maximum

voltage of the EN pin of 6 V.

TP8

AGND_U1

U1

AGND test point

TP9

BODE_U1

U1

Test point between voltage divider network and output voltage. Used for Bode plot

measurements.

TP10

VOUT_U1

U1

SMB connector to measure output voltage. When using this test point, the scope should

be set for 1-MΩ termination. When using 50-Ω termination, a 2:1 divider is created.

TP11

VIN

Both

VIN test point near input terminals

TP12

VIN_U2

U2

VIN test point. Use this for efficiency measurements.

TP13

SW_U2

U2

SW node solder mask opening

TP14

SW_U2

U2

SW node test point

TP15

VOUT_U2

U2

VOUT test point. Use this for efficiency, output regulation, and bode plot measurements.

TP16

PGND_U2

U2

PGND test point

TP17

PGND_EFF_U2

U2

PGND test point. Use this for efficiency measurements.

TP18

PGOOD_U2

U2

PGOOD test point

TP19

PGND

Both

PGND test point near input terminals

TP20

AGND_U2

U2

AGND test point

TP21

BP5_U2

U2

BP5 test point

TP22

BODE_U2

U2

Test point between voltage divider network and output voltage. Used for Bode plot

measurements.

TP23

EN_U2

U2

EN test point. If you are applying an external voltage, it must be kept below the absolute

maximum voltage of the EN pin of 6 V.

TP24

VO_ADJ

U2

Test point for injecting current into the FB divider to adjust the DC output voltage or inject a

step to FB to test OVP

TP25

VO_2NDSTG

U2

Test point to measure output voltage after second stage filter if added to EVM.

TP26

SYNC

Both

SYNC test point. Supply an external clock to this test point to synchronize both regulators

to it.

TP27

FSEL

U2

FSEL test point

TP28

SW_U2

U2

SMB connector to measure SW node. When using this test point, the scope should be

set for 50-Ω termination. The combination of 50-Ω termination and 450-Ω series resistance

creates a 10:1 attenuation.

TP29

VOUT_U2

U2

SMB connector to measure output voltage. When using this test point, the scope should

be set for 1-MΩ termination. When using 50-Ω termination, a 2:1 divider is created.

TP30

VO_2NDSTG

U2

SMB connector to measure output voltage after second stage filter if added to EVM. When

using this test point, the scope should be set for 1-MΩ termination. When using 50-Ω

termination, a 2:1 divider is created.

TP31

FGEN

Both

Test point to connect function generator to load transient circuit. Slowly increase amplitude

and vary slew rate of function generator for desired load step.

TP32

ISNS

Both

Test point to measure current in load transient circuit. Gain is 10 A/V.

TP33

PGND

Both

PGND test point for load transient circuit

TP34

MODE

U2

MODE test point

Test Setup and Results

10

TPS543320 SWIFT™ Step-Down Converter Evaluation Module User's Guide

SLVUC07A – DECEMBER 2020 – REVISED MAY 2021

Copyright © 2021 Texas Instruments Incorporated