Conversation Between the TLV1562 and the DSP

17

Interfacing the TLV1562 Parallel ADC to the TMS320C54x DSP

7.6

Dual Continuous Mode

The dual continuous mode provides a data stream of two input signals. The

characteristic of the data protocol is similar to the mono continuous mode but with

the use of two RD cycles for one sample/hold cycle.

CAUTION:

In this mode, the sampling result sent out by the ADC is the

value of the sample from the last cycle. Therefore, the first

sample after initialization is trash.

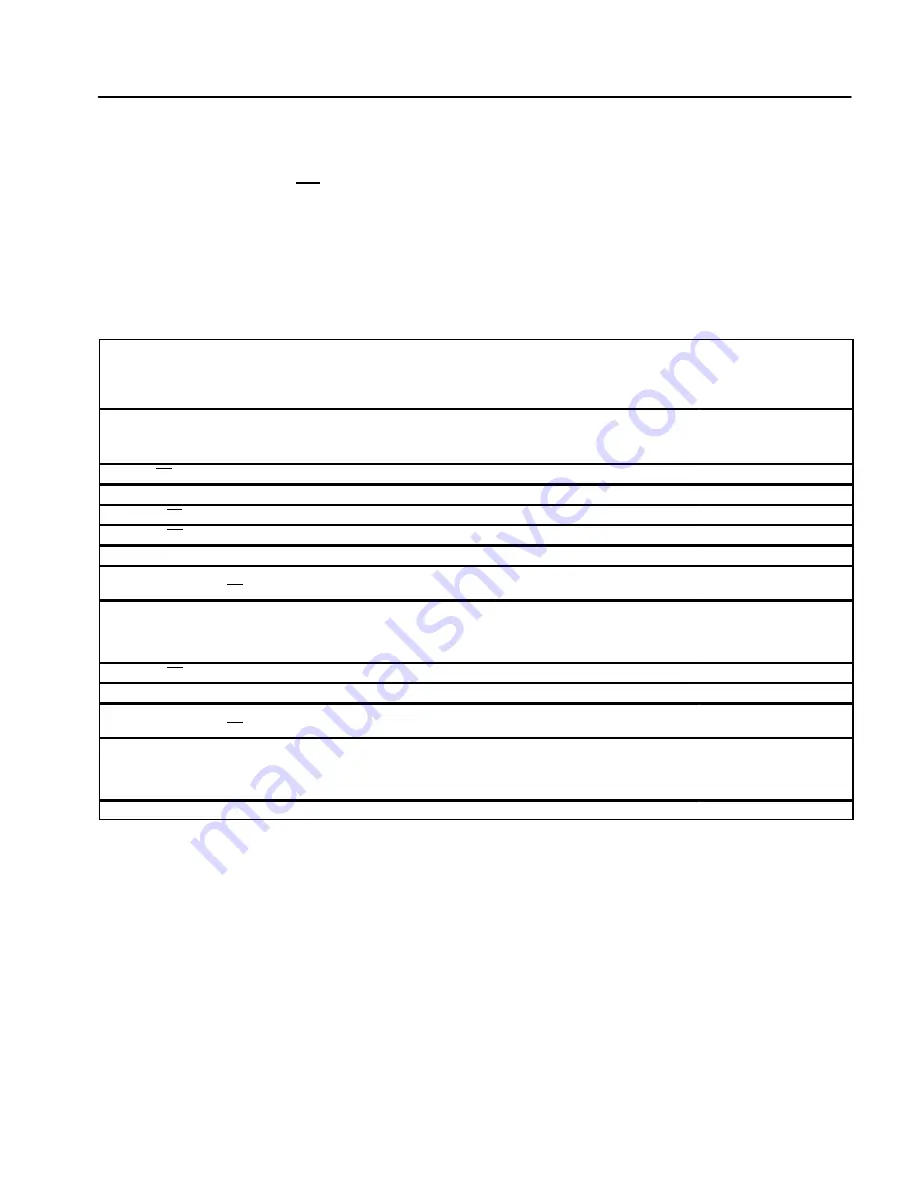

Table 11. DSP Algorithm for Dual Continuous Mode

Wait cycles for the DSP internally (40MHz DSPCLK):

STEPS

TIMING, NOTES

APD=0

ADCSYCLK

= 7.5 MHz

APD=0

ADCSYCLK

= 10 MHz

APD=1

ADCSYCLK

= 10 MHz

APD=1

ADCSYCLK

= 10 MHz

0.

Initialization

N/A

N/A

Write all configuration data to the

ADC

Activate the dual continuous mode in

CR0(2;3)

N/A

N/A

1.

Set CS

deselect ADC

N/A

N/A

2.

Wait for t

(SAMPLE1)

t

(SAMPLE1)

= 100 ns

≥

4

≥

4

N/A

N/A

3.

Clear CS

Select ADC

N/A

N/A

4.

Clear RD

Start conversion

5.

Wait the time t

EN(DATAOUT)

t

EN(DATAOUT)

= 41 ns

≥

2

≥

2

N/A

N/A

6.

Read first sample out from the

data port; reset RD signal

(Caution: the first result after initialization

is trash)

N/A

N/A

7.

Wait for the time t

(CONV1)

minus

step 7 and 8 to ensure 5(6) ADC-

SYSCLk

t

(CONV1)

= 5(6) ADCSysclk; since step 7

and 8 take at least 4 DSPSYSCLK, the

calculation are 5(6)ADCSYSCLK minus

100 ns

≥

23

≥

16

N/A

N/A

8.

Clear RD

Start conversion

9.

Wait the time t

EN(DATAOUT)

t

EN(DATAOUT)

= 41 ns

≥

2

≥

2

N/A

N/A

10.

Read second sample out from the

data port; reset RD signal

(Caution: the first result after initialization

is trash)

N/A

N/A

11.

Wait for the time t

(CONV1)

minus

step 7 and 8 to ensure 5(6) ADC-

SYSCLk

t

(CONV1)

= 5(6) ADCSysclk; since step 7

and 8 take at least 4 DSPSYSCLK, the

calculation are 5(6)ADCSYSCLK minus

100ns

≥

23

≥

16

N/A

N/A

12.

Go to step 4 for more samples

N/A

N/A

Summary of Contents for TLV1562

Page 6: ...vi SLAA040 ...