(All the conditions for assertion are valid and

DSI_CLK_CTRL[18] HS_AUTO_STOP_ENABLE = 0x1)

Or

(DSI_CLK_CTRL[19] HS_MANUAL_STOP_CTRL = 0x1 and

DSI_CLK_CTRL[18] HS_AUTO_STOP_ENABLE = 0x0)

One of the conditions for de-assertion is valid and

DSI_CLK_CTRL[18] HS_AUTO_STOP_ENABLE = 0x1)

Or

(DSI_CLK_CTRL[19] HS_MANUAL_STOP_CTRL = 0x0 and

DSI_CLK_CTRL[18] HS_AUTO_STOP_ENABLE = 0x0)

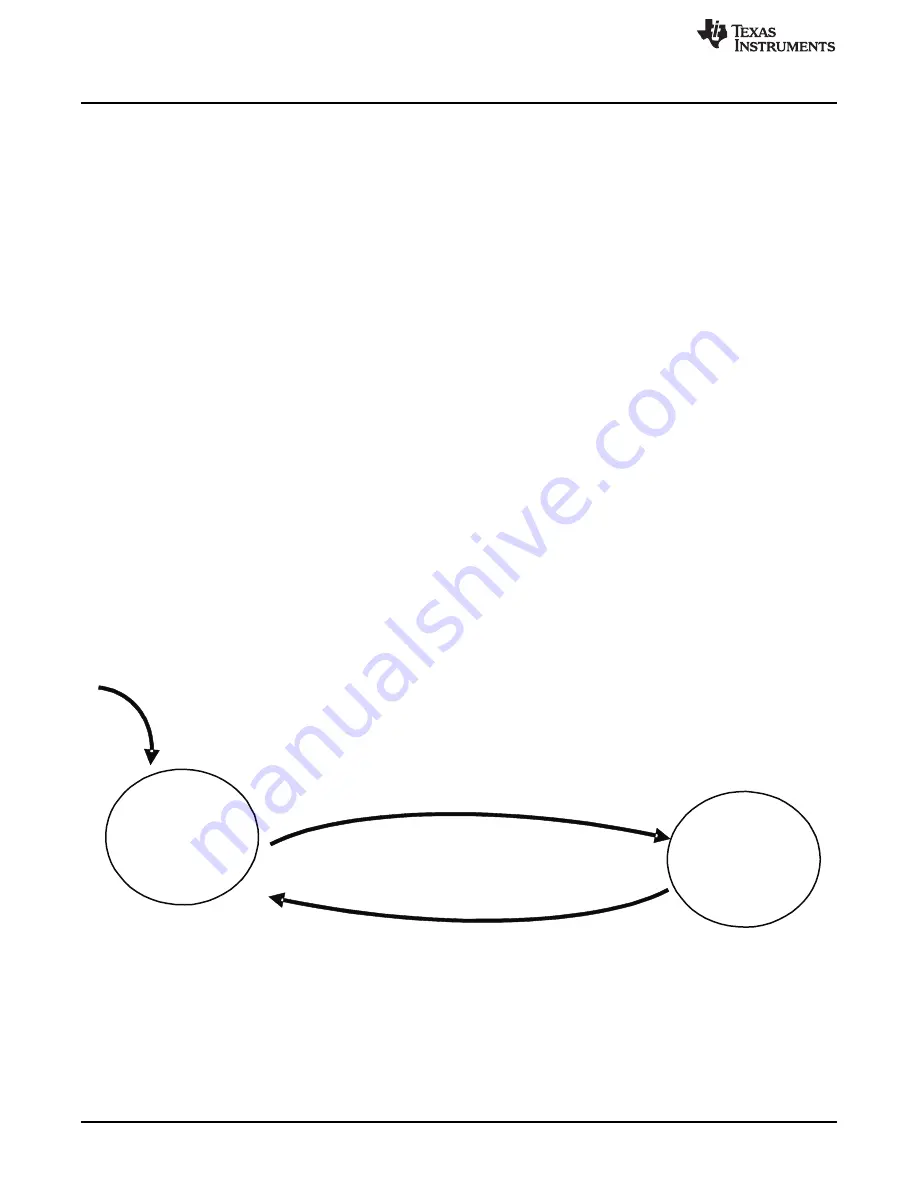

RESET

DSIStopClk

De-Assertion

DSIStopClk

Assertion

dss-171

Public Version

Display Subsystem Functional Description

www.ti.com

When the interface is disabled (that is, DSS.

[0] IF_EN bit set to 0), the signal DSIStopClk is

asserted.

The assertion of the DSIStopClk depends on the following conditions:

•

Clock lane TxRequestHS is deasserted (the DDR clock on the clock lane is not required anymore).

The get TxRequestHS deassertion, all of the following conditions are required:

–

The DSS.

[13] DDR_CLK_ALWAYS_ON bit must be reset to 0 and no HS data

transfer should be ongoing or already scheduled.

–

No VC active in video mode. No VC using the video mode is enabled; if the VC is enabled, the

mode is command mode only (that is, DSS.

[0] VC_EN bit set to 1 and

[4] MODE bit set to 0).

–

No command mode requiring high-speed transfer (one or more VCs using command mode can be

active)

–

Or DSS.

[0] IF_EN bit reset to 0 (if all previous conditions are not required)

The deassertion of the DSIStopClk depends on one of the following conditions (the DSI interface is

enabled by setting the DSS.

[0] IF_EN bit to 1):

•

Clock lane TxRequestHS must be asserted (the DDR clock on the clock lane is required anymore).

•

One video mode VC active

•

At least one VC in command mode requiring high-speed transfer

•

The DSS.

[13] DDR_CLK_ALWAYS_ON bit is set to 1 by software users (the

DSS.

[0] IF_EN bit must be reset to 0 to update the DDR_CLK_ALWAYS_ON bit value)

Automatic assertion/deassertion is enabled by using the DSS.

HS_AUTO_STOP_ENABLE bit.

Manual mode can be used by setting/resetting the DSS.

[19] HS_MANUAL_STOP_CTRL

bit to assert/deassert the DSIStopClk signal.

7.4.3.6.2.1.2 DSI-PLL HS Clock FSM

shows the DSI PLL HS clock FSM.

Figure 7-95. DSI PLL HS Clock FSM

When DSIStopClk is used there is a latency through other modules (DSI PLL controller and DSI_PHY)

1674

Display Subsystem

SWPU177N – December 2009 – Revised November 2010

Copyright © 2009–2010, Texas Instruments Incorporated