www.ti.com

Board Layout

27

SNVU472A – October 2016 – Revised February 2017

Submit Documentation Feedback

Copyright © 2016–2017, Texas Instruments Incorporated

The LP8756xQ1EVM Evaluation Module

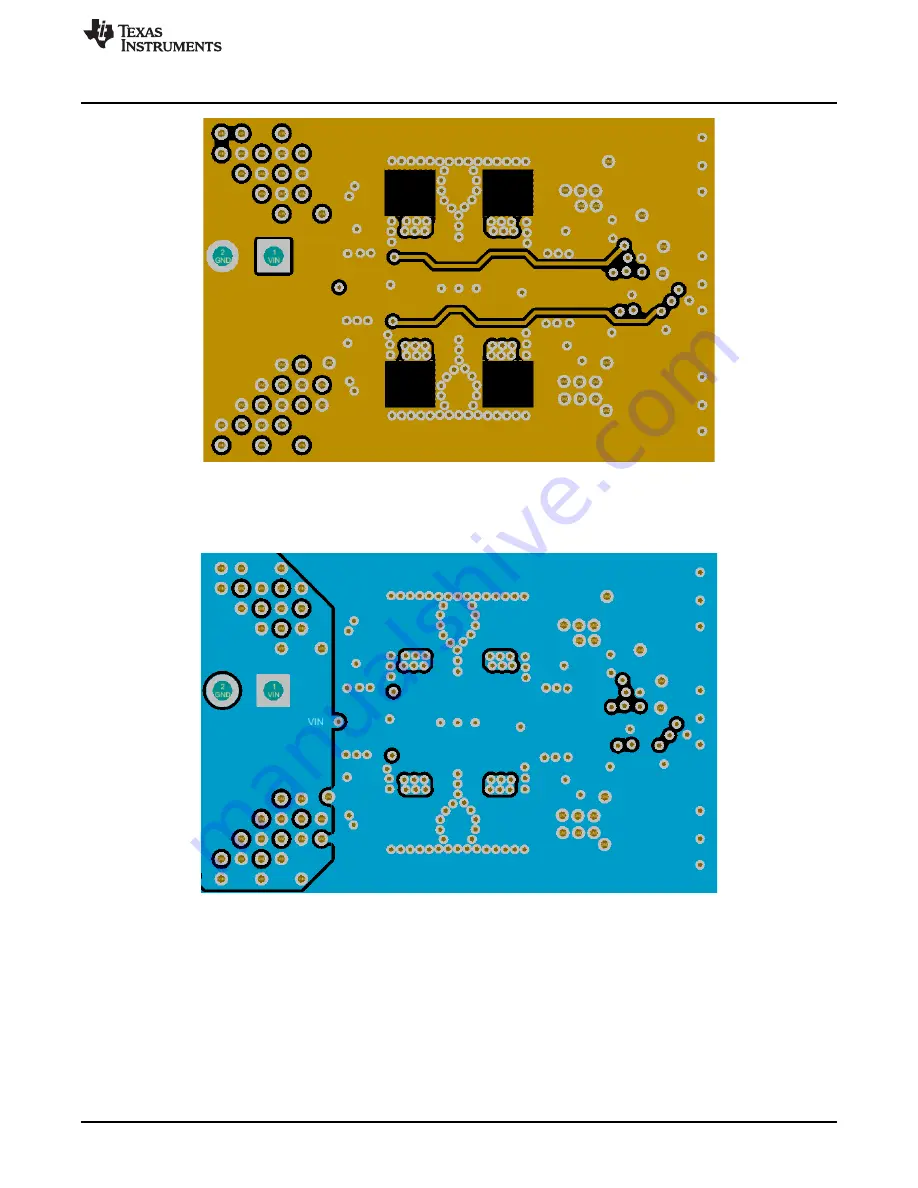

GND plane close to top layer (0.063 mm) helps to reduce parasitic inductance. Holes in the plane are under inductor footprint (SW

node) to reduce parasitic capacitance of the SW node, thus reducing noise coupling and improving efficiency.

Figure 24. Mid-Layer1

VIN supply is routed in this layer between the ground planes to reduce radiated emissions. VIN and GND vias are placed in hatched

pattern to avoid large gaps in these planes.

Figure 25. Mid-Layer2