LP8752_EVM_mid3_layer

Board Layout

www.ti.com

26

SNVU472A – October 2016 – Revised February 2017

Submit Documentation Feedback

Copyright © 2016–2017, Texas Instruments Incorporated

The LP8756xQ1EVM Evaluation Module

Figure 22. Component Placement Bottom Layer

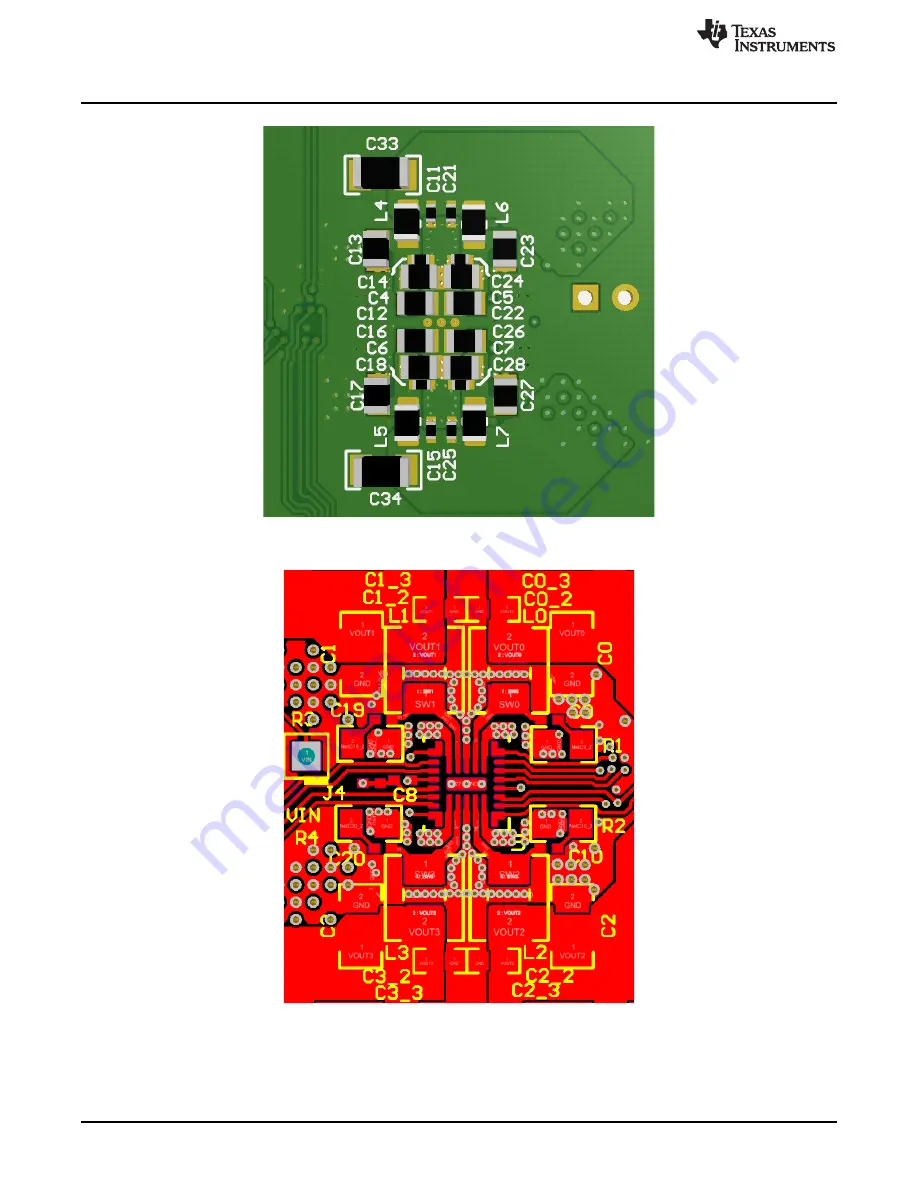

VIN nets are connected to bottom layer with multiple vias. This allows closer placement of the inductors, thus

reducing SW node size and EMI. Also snubber circuits are placed next to SW nets for EMI reduction. Multiple GND

vias are used to provide solid ground around the LP8756xQ1 device.

Figure 23. Top Layer