6.

Disable I2C PASS-THROUGH ALL by setting deserializer register reg_0x05[7]=0

INPUT RxCLKIN LOSS DETECT

The serializer can be programmed to enter a low power SLEEP state when the input clock (PCLK) is lost. A clock loss condition is

detected when PCLK drops below approximately 1MHz. When a PCLK is detected again, the serializer will then lock to the incoming

RxCLKIN±. Note – when RxCLKIN± is lost, the optional Serial Bus Control Registers values are still retained. See (

more information.

SERIAL LINK FAULT DETECT

The DS90UH927Q can detect fault conditions in the FPD-Link III interconnect. If a fault condition occurs, the Link Detect Status is

0 (cable is not detected) on bit 0 of address 0x0C (

). The DS90UH927Q will detect any of the following conditions:

1.

Cable open

2.

“

+” to “-” short

3.

”+” to GND short

4.

”-” to GND short

5.

”+” to battery short

6.

”+” to battery short

7.

Cable is linked incorrectly (DOUT+/DOUT- connections reversed)

Note: The device will detect any of the above conditions, but does not report specifically which one has occurred.

LOW FREQUENCY OPTIMIZATION (LFMODE)

The LFMODE is set via register (

) or LFMODE Pin. This mode optimizes device operation for lower input data clock ranges

supported by the serializer. If LFMODE is Low (LFMODE = 0, default), the RxCLKIN± frequency is between 15MHz and 85MHz.

If LFMODE is High (LFMODE = 1), the RxCLKIN± frequency is between 5 MHz and <15 MHz. Note: when the device LFMODE is

changed, a PDB reset is required. When LFMODE is high (LFMODE=1), the line rate relative to the input data rate is multiplied by

four. Thus, for the operating range of 5MHz to <15MHz, the line rate is 700Mbps to <2.1Gbps with an effective data payload of

175Mbps to 525Mbps. Note: for Backwards Compatibility Mode (BKWD=1), the line rate relative to the input data rate remains the

same.

INTERRUPT PIN (INTB)

1.

On the DS90UH927Q serializer, set register reg_0xC6[5] = 1 and 0xC6[0] = 1 (

) to configure and arm the interrupt.

2.

When INTB_IN on the deserializer (DS90UH926Q or DS90UH928Q) is set LOW, the INTB pin on the serializer also pulls low,

indicating an interrupt condition.

3.

The external controller detects INTB = LOW and reads the HDCP_ISR register (

) to determine the interrupt source.

Reading this register also clears and resets the interrupt.

GENERAL-PURPOSE I/O

GPIO[3:0]

In normal operation, GPIO[3:0] may be used as general purpose IOs in either forward channel (inputs) or back channel (outputs)

applications. GPIO modes may be configured from the registers (

). GPIO[1:0] are dedicated pins and GPIO[3:2] are shared

with I2S_DC and I2S_DD respectively. Note: if the DS90UH927Q is paired with a DS90UH926Q deserializer, the devices must be

configured into 18-bit mode to allow usage of GPIO pins on the DS90UH927 serializer. To enable 18-bit mode, set serializer register

reg_0x12[2] = 1. 18-bit mode will be auto-loaded into the deserializer from the serializer. See

figuration.

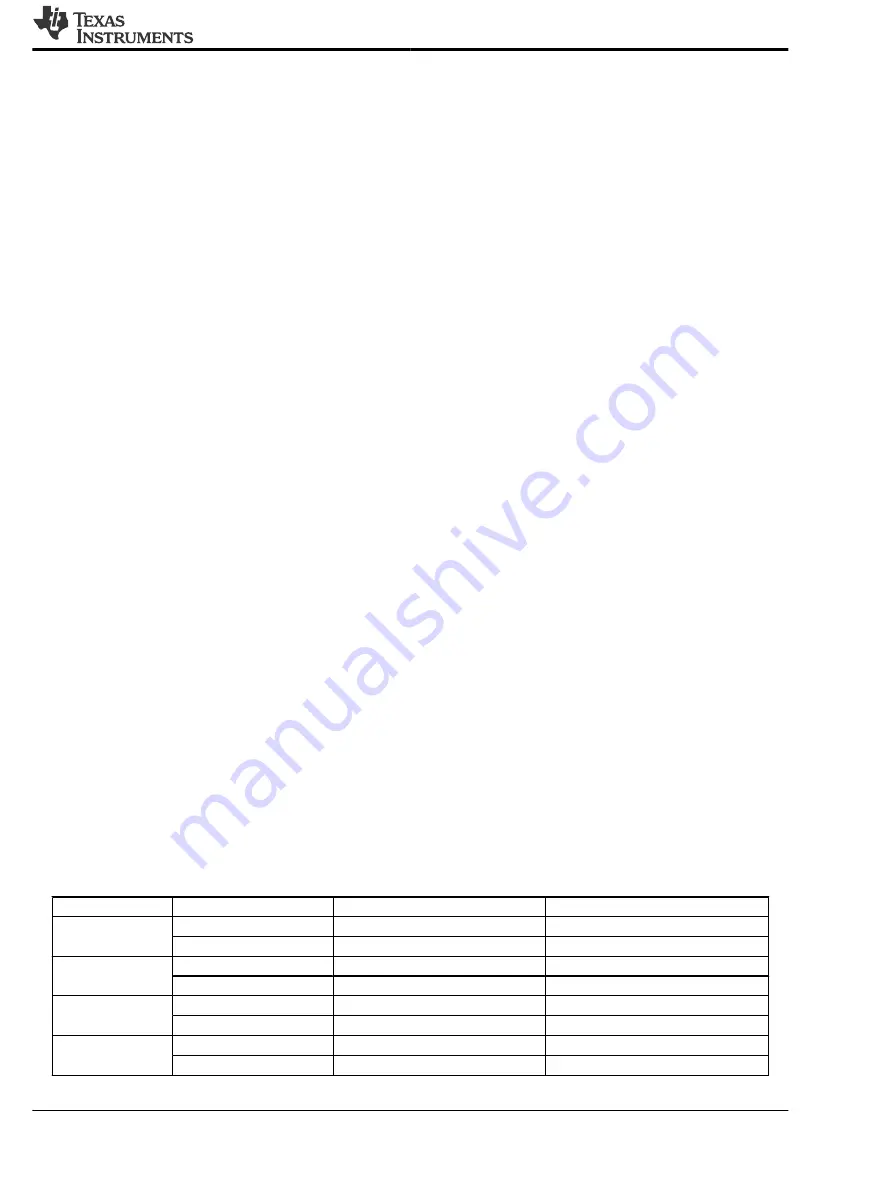

TABLE 1. GPIO Enable and Configuration

Description

Device

Forward Channel

Back Channel

GPIO3

DS90UH927Q

0x0F = 0x03

0x0F = 0x05

DS90UH926/8Q

0x1F = 0x05

0x1F = 0x03

GPIO2

DS90UH927Q

0x0E = 0x30

0x0E = 0x50

DS90UH926/8Q

0x1E = 0x50

0x1E = 0x30

GPIO1

DS90UH927Q

0x0E = 0x03

0x0E = 0x05

DS90UH926/8Q

0x1E = 0x05

0x1E = 0x03

GPIO0

DS90UH927Q

0x0D = 0x03

0x0D = 0x05

DS90UH926/8Q

0x1D = 0x05

0x1D = 0x03

DS90UH927Q

Copyright © 1999-2012, Texas Instruments Incorporated

19