ADC

4.096 V

REF

REFCAP

REFIO

AGND

22

P

F

REFGND

C

REF

REFSEL

AVDD

REF5040

(See the device datasheet for

a detailed pin configuration.)

AVDD

OUT

DVDD

1

P

F

SBAS686 – JULY 2015

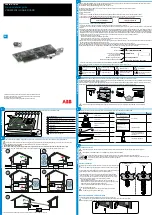

8.3.8.2 External Reference

For applications that require a better reference voltage or a common reference voltage for multiple devices, the

ADS8694 and ADS8698 offer a provision to use an external reference along with an internal buffer to drive the

ADC reference pin. In order to select the external reference mode, either tie the REFSEL pin high or connect this

pin to the DVDD supply. In this mode, an external 4.096-V reference must be applied at REFIO (pin 5), which

becomes an input pin. Any low-power, low-drift, or small-size external reference can be used in this mode

because the internal buffer is optimally designed to handle the dynamic loading on the REFCAP pin, which is

internally connected to the ADC reference input. The output of the external reference must be appropriately

filtered to minimize the resulting effect of the reference noise on system performance. A typical connection

diagram for this mode is shown in

Figure 62. Device Connections for Using an External 4.096-V Reference

The output of the internal reference buffer appears at the REFCAP pin. A minimum capacitance of 10 µF must

be placed between REFCAP (pin 7) and REFGND (pin 6). Place another capacitor of 1 µF as close to the

REFCAP pin as possible for decoupling high-frequency signals. Do not use the internal buffer to drive external ac

or dc loads because of the limited current output capability of this buffer.

28

Copyright © 2015, Texas Instruments Incorporated

Product Folder Links: