INB

( J7 )

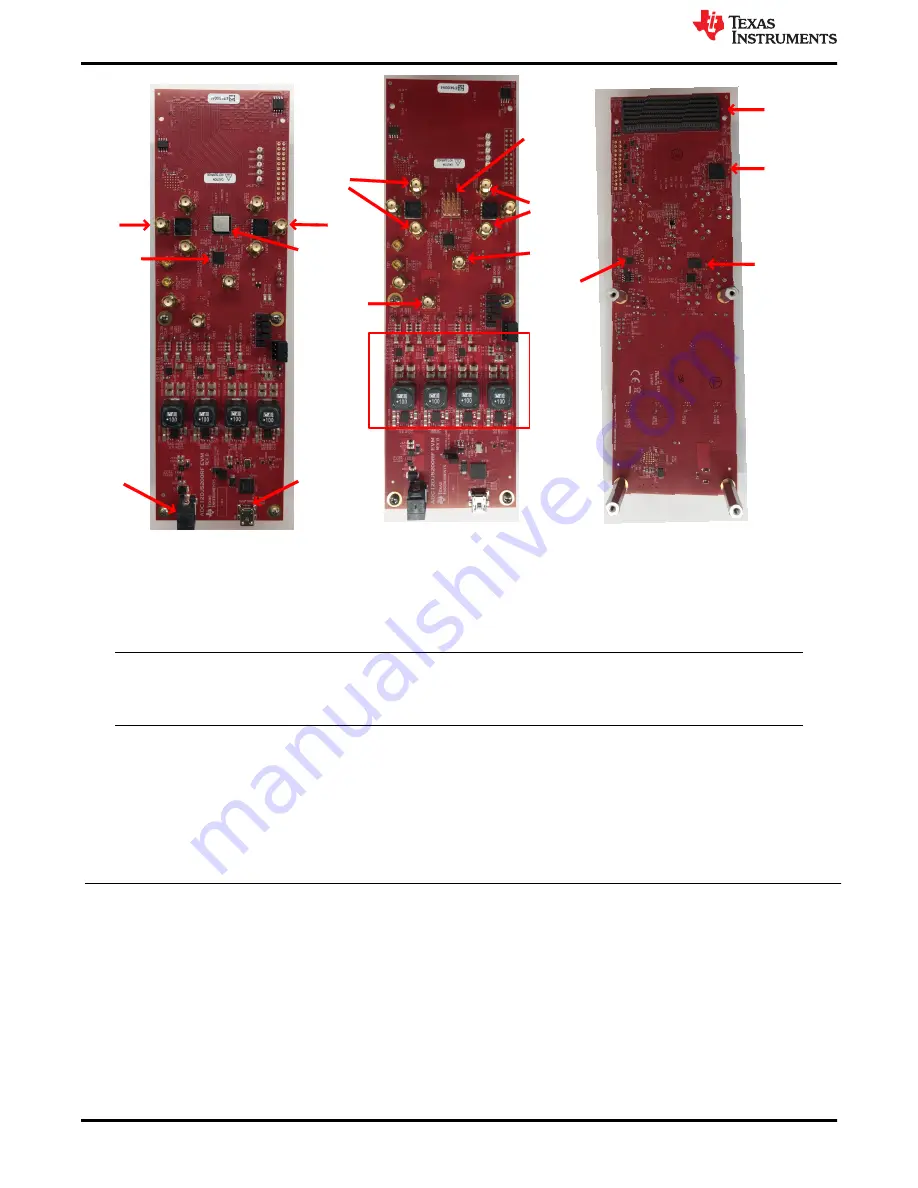

ADC12DJ5200RF

ADC12DJ5200RF EVM top side

without heat sink installed

INA

( J4 )

USB

Connector

+12V DC

ADC12DJ5200RF EVM top side with

heat sink installed

Power (DC/DC

DQG /'2¶V

)

External device

Clock input ( J10 )

INB+/-

INA+/-

External reference

clock input ( J17 )

FMC+

connector

LMK04828

LMK61E2

ADC12DJ5200RF EVM bottom side

LM95233

Heat Sink for the ADC

Copyright © 2016, Texas Instruments Incorporated

LMX2594

Figure 1-1. EVM Orientation

The digital data from the ADCxxDJxx00RFEVM board is quickly and easily captured with the TSW14J57EVM

data capture boards.

Note

The TSW14J57EVM cannot be used for JMODES that use 64b/66b encoding, or serial rates above 15

Gbps.

The TSW14J57EVM captures the high-speed serial data, decodes the data, stores the data in memory, and then

uploads it to a connected PC through a USB interface for analysis. The High-Speed Data Converter Pro (HSDC

Pro) software on the PC communicates with the hardware and processes the data.

With proper hardware selection in the HSDC Pro software, the TSW14J57 device is automatically configured to

support a wide range of operating speeds of the ADCxxDJxx00RFEVM, but the device may not cover the full

operating range of the ADC device. Serial data rates of 15 Gbps down to 1 Gbps are supported.

2

ADCxxDJxx00RF Evaluation Module

SLAU640A – APRIL 2019 – REVISED JUNE 2021

Copyright © 2021 Texas Instruments Incorporated