Alternate Hardware Configurations

5

Alternate Hardware Configurations

This section describes alternate hardware configurations that can be used for customized evaluation.

5.1

Clocking Options

By default, the ADC requires a clock source from an external signal generator. Optionally, the EVM may

be configured such that the ADC is provided a clock signal by the LMK04828.

5.1.1

Providing the ADC Sampling Clock from the LMK04828

The EVM may be reconfigured to route a clock from the LMK04828 to the ADC14X250 to be used as the

device clock. This configuration represents a more realistic system configuration but the data conversion

noise performance is affected by the noise of the clock signal from the LMK device. The EVM must be

changed from the default configuration in the following ways:

•

Remove R40, R41

•

Place R43 and R50 with 0402, 0-

Ω

resistors

•

Remove R227

•

Configure the LMK04828 to output an LVPECL clock on the DCLKout2 output

•

The reference clock for the LMK04828 must be provided via the EXTREF input connector (J7)

5.1.2

Recommended LMK04828 Configurations

The LMK04828 can be used in a number of useful configurations to provide the necessary clocks for the

ADC and JESD204B interface as described in

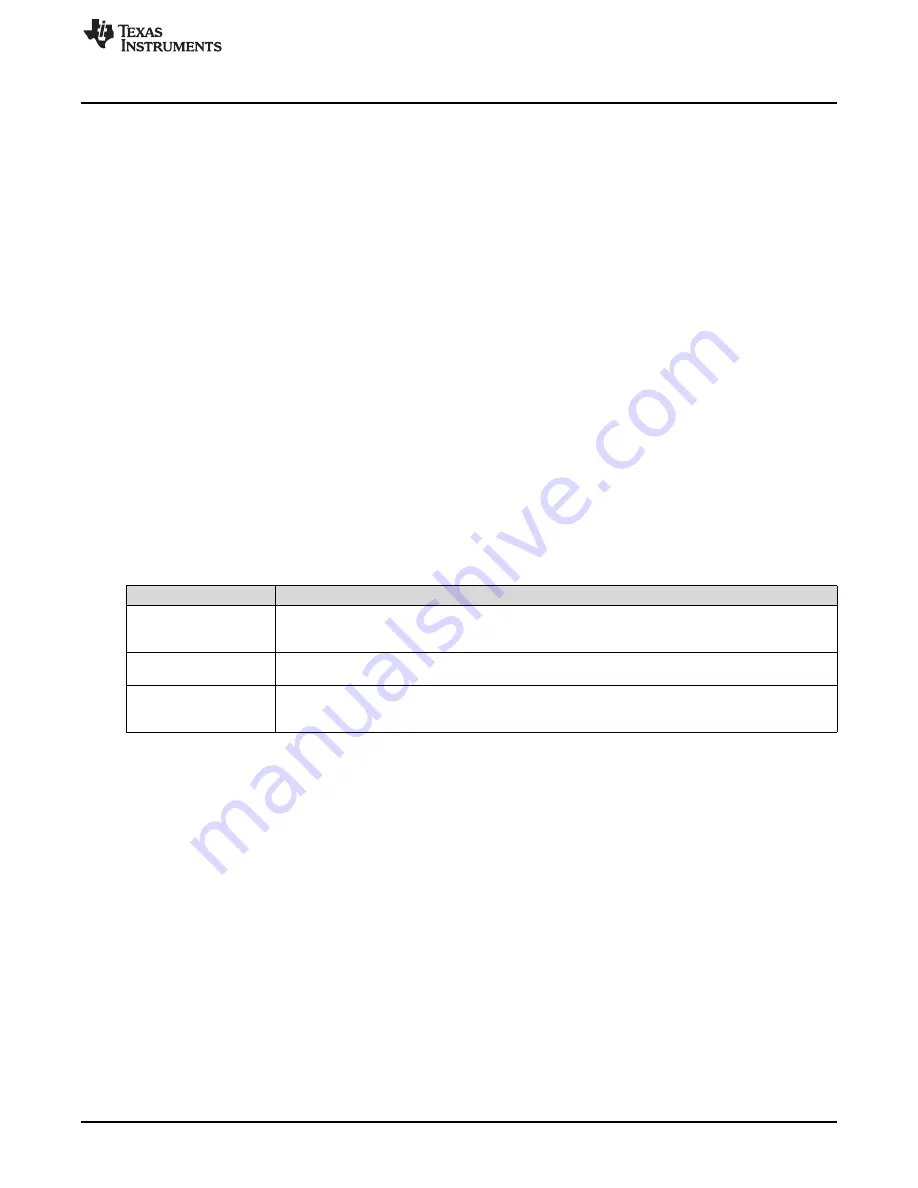

Table 6. Recommended LMK04828 Configurations

Mode

Description

Clock distribution mode

Input reference is distributed to clock outputs and the frequency is divided, if desired. Frequency

multiplication is not supported. Input reference must be provided to CLKin1 input via CLK (J4) and R21

or via EXTREF (J7).

Clock Multiplier Mode

Input reference is locked to internal VCO, allowing frequency integer-N multiplication from input to

(PLL2 Only)

output. Reference must be provided at OSCin input via EXTREF or on-board XO at Y3.

Jitter Cleaner and Clock

Input reference is cleaned with very low bandwidth PLL1 and then multiplied to the desired frequency

Multiplier

using PLL2. Reference must be provided at CLKin1 input or on-board XO at Y1/Y2. On-board VCXO at

Mode (PLL1 + PLL2)

Y3 is also required.

13

SLAU625 – November 2015

ADC14X250EVM Evaluation Module

Copyright © 2015, Texas Instruments Incorporated