Specifications

3–14

TMS 540 PowerPC 60X Microprocessor Support Instruction Manual

T1

T2

T3

T4

T5

T6

SYSCLK

TS*

TA*/TEA*

XATS*

Master sample points

Sample point

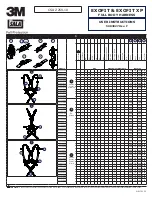

Figure 3–2: PowerPC 60X bus timing

T1 Clock Edge.

The BG*, ABB*, and ARTRY* signals are logged in on this clock

edge.

T2 Clock Edge.

The A31-A0, TT3-TT1, TSIZ2-TSIZ0, XATS*, TBST*, TS*,

TC0, SYSCLK, DBG*, DRTRY_ERLY*, DBWO*, and ARTRY_DATA* signals

are logged in on this clock edge.

T3 Clock Edge.

The DH31-DH0, DL31-DL0, TEA*, TA*, TT0, DBB*, AACK*,

ARTRY*, DRTRY*, BR*, APE*, GBL*, BG*, ABB*, ARTRY_ERLY*, and

XATS_B2* signals are logged in on this clock edge. Signals logged in on the T2

clock edge are also logged in except the A31-A0 signals.

T4 Clock Edge.

The A31-A0, TT3-TT1, TSIZ2-TSIZ0, XATS*, TBST*, TS*,

TC0, SYSCLK, DBG*, DRTRY_ERLY*, DBWO*, ARTRY_DATA*, BG*,

ABB*, ARTRY_ERLY*, and XATS_B2 signals are logged in on this clock edge.

T5 Clock Edge.

The A31-A0, TT3-TT1, TSIZ2-TSIZ0, XATS*, TBST*, TS*,

TC0, SYSCLK, DBG*, DRTRY_ERLY*, DBWO*, and ARTRY_DATA* signals

are logged in on this clock edge.

T6 Clock Edge.

The DH31-DH0, DL31-DL0, TEA*, TA*, TT0, DBB*, AACK*,

ARTRY*, DRTRY*, BR*, APE*, GBL*, BG*, ABB*, ARTRY_ERLY*, and

XATS_B2* signals are logged in on this clock edge. Signals logged in on the T5

clock edge are also logged in except the A31-A0 signals.

The clocking algorithm for the PowerPC 60X microprocessor support has two

variations: DRTRY Cycles Included or DRTRY Cycles Excluded.

Clocking Options