Spectrum Signal Processing

Monaco Technical Reference

VME64 Bus Interface

Part Number 500-00191

25

Revision 2.00

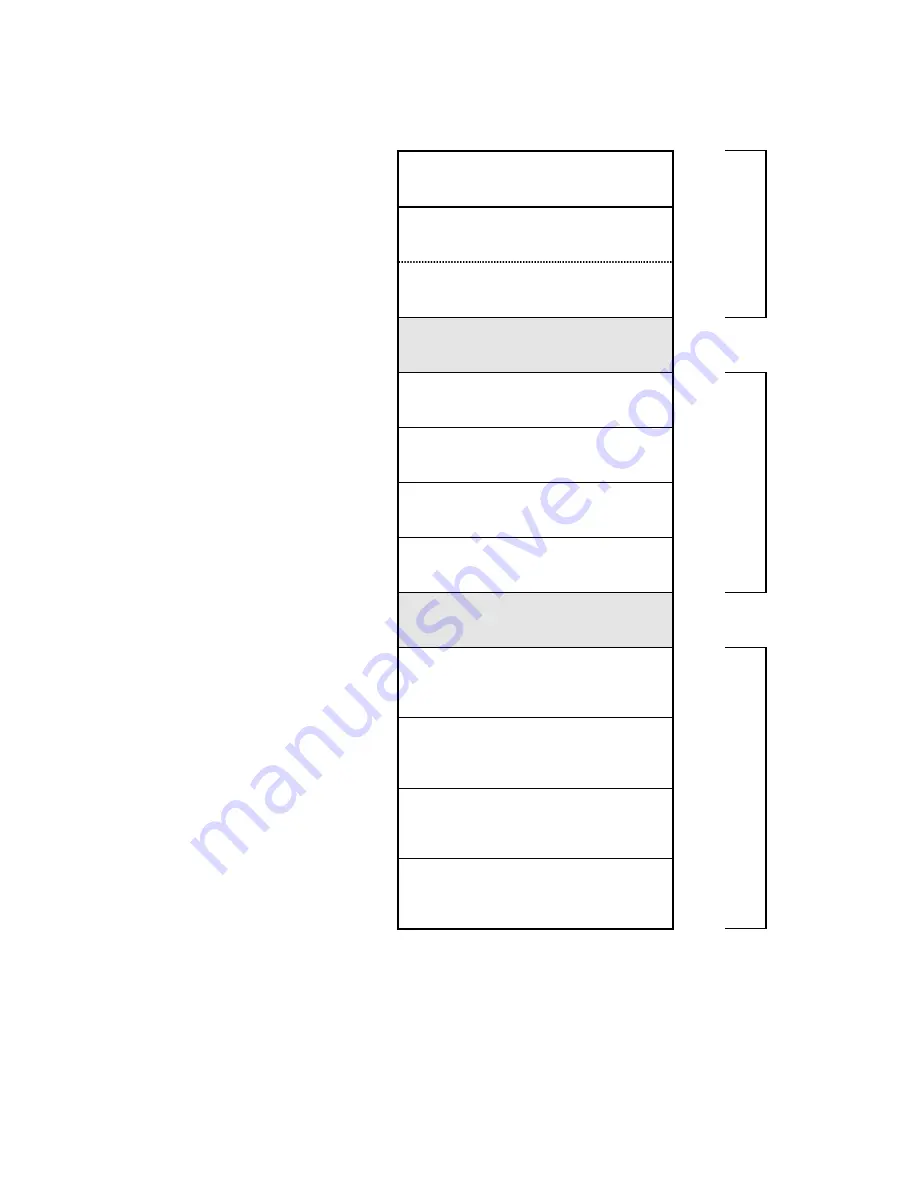

VME Offset Address

00 0000h

Test Bus Controller Registers (JTAG)

00 0FFFh

00 1000h

VME A24 Status Register (Read Only)

FPGA

00 1003h

00 1004h

VME A24 Control Register (Read/Write)

00 1007h

00 1008h

Reserved

00 1FFFh

00 2000h

Node A HPI Registers

00 2FFFh

00 3000h

Node B HPI Registers

00 3FFFh

‘C6x

00 4000h

Node C HPI Registers

00 4FFFh

00 5000h

Node D HPI Registers

00 5FFFh

00 6000h

Reserved

00 FFFFh

01 0000h

Node A HPID DMA Space (HPIA incremented)

all addresses mapped to 00 2008h

16 KB

01 3FFCh

01 4000h

Node B HPID DMA Space (HPIA incremented)

all addresses mapped to 00 3008h

16 KB

01 3FFCh

‘C6x

01 B000h

Node C HPID DMA Space (HPIA incremented)

all addresses mapped to 00 4008h

16 KB

01 3FFCh

01 C000h

Node D HPID DMA Space (HPIA incremented)

all addresses mapped to 00 5008h

16 KB

01 FFFCh

Figure 9 A24 Secondary Interface Memory Map

Refer to the JTAG Debugging chapter for information on using the Test Bus Controller

for JTAG operation. The

VME A24 Status Register

and the

VME A24 Control Register

are described in the Registers chapter.