4

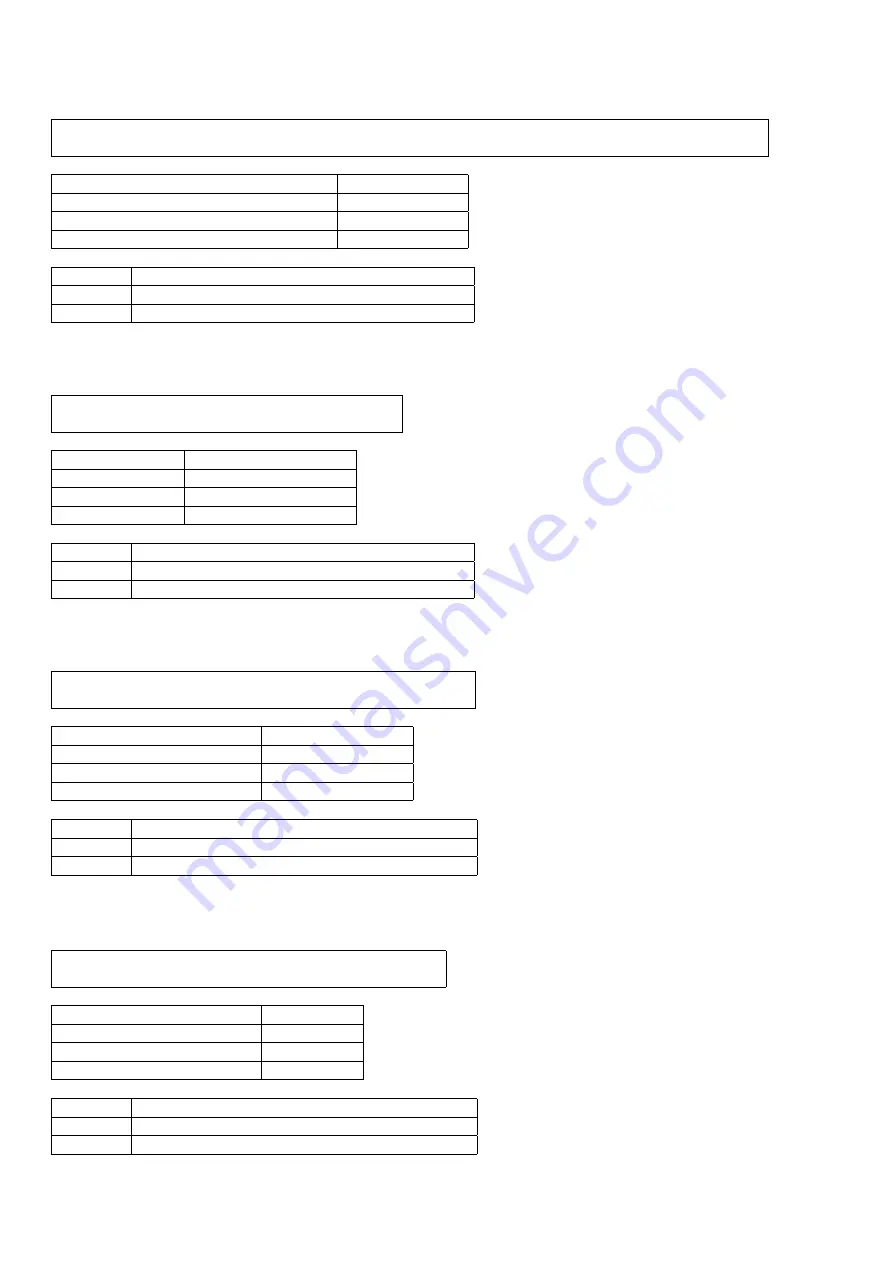

CPU OVERVIEW

39

4.8.25

vhdp

vhdp

VectorHomogenousDotProduct (Pair/Triple/Quad)

vfpu_regs[%vfpu_rd] <- homogenousdotproduct(vfpu_regs[%vfpu_rs], vfpu_regs[%vfpu_rt])

vhdp.p %vfpu_rd, %vfpu_rs, %vfpu_rt

Dot Product Pair

vhdp.t %vfpu_rd, %vfpu_rs, %vfpu_rt

Dot Product Triple

vhdp.q %vfpu_rd, %vfpu_rs, %vfpu_rt

Dot Product Quad

%vfpu_rt

VFPU Vector Source Register ([s|p|t|q]reg 0..127)

%vfpu_rs

VFPU Vector Source Register ([s|p|t|q]reg 0..127)

%vfpu_rd

VFPU Vector Destination Register ([s|p|t|q]reg 0..127)

4.8.26

vidt

vidt

VectorLoadIdentity (Pair/Triple/Quad)

vfpu_regs[%vfpu_rd] <- identity vector

vidt.p %vfpu_rd

Set 2x1 Vector to Identity

vidt.t %vfpu_rd

Set 3x1 Vector to Identity

vidt.q %vfpu_rd

Set 4x1 Vector to Identity

%vfpu_rd

VFPU Vector Destination Register ([s|p|t|q]reg 0..127)

4.8.27

vabs

vabs

AbsoluteValue (Single/Pair/Triple/Quad)

vfpu_regs[%vfpu_rd] <- abs(vfpu_regs[%vfpu_rs])

vabs.s %vfpu_rd, %vfpu_rs

Absolute Value Single

vabs.p %vfpu_rd, %vfpu_rs

Absolute Value Pair

vabs.t %vfpu_rd, %vfpu_rs

Absolute Value Triple

vabs.q %vfpu_rd, %vfpu_rs

Absolute Value Quad

%vfpu_rd

VFPU Vector Destination Register (m[p|t|q]reg 0..127)

%vfpu_rs

VFPU Vector Source Register (m[p|t|q]reg 0..127)

4.8.28

vneg

vneg

Negate (Single/Pair/Triple/Quad)

vfpu_regs[%vfpu_rd] <- -vfpu_regs[%vfpu_rs]

vneg.s %vfpu_rd, %vfpu_rs

Negate Single

vneg.p %vfpu_rd, %vfpu_rs

Negate Pair

vneg.t %vfpu_rd, %vfpu_rs

Negate Triple

vneg.q %vfpu_rd, %vfpu_rs

Negate Quad

%vfpu_rd

VFPU Vector Destination Register (m[p|t|q]reg 0..127)

%vfpu_rs

VFPU Vector Source Register (m[p|t|q]reg 0..127)

Summary of Contents for PlayStationPortable

Page 114: ...12 AUDIO PROCESSING 114 12 Audio Processing 12 1 Overview 44100 Hz Sample Frequency ...

Page 116: ...14 WLAN 116 14 WLAN ...

Page 117: ...15 USB PORT 117 15 USB Port ...

Page 118: ...16 UMD 118 16 UMD ...

Page 119: ...17 MEMORY STICK 119 17 Memory Stick ...

Page 128: ...21 FLASH MEMORY STRUCTURE FLASH1 128 21 Flash Memory Structure flash1 DIC REGISTRY VSH THEME ...

Page 141: ...28 IPL 141 28 IPL ...