- 17 -

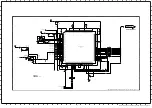

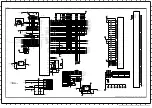

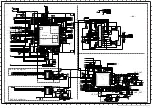

4-1. BLOCK DIAGRAM

One chip

(Main micro)

(Video decoder)

(Sound decoder)

(Backend control)

Panel

240/200Hz

Power Supply

Gx/IPx

Aerial/Cable

DVI/PC in

SCART/V1

SCART/V2

Audio Out

Opt. Out

Comp1

Tuner

USB

C

I

PC In

PHY

MS (JIG)

BA

Ether

Audio

Pre Amp

Audio

DSP

Video SW

DDR2

1 Gb

Sub micro

Sub Chrom

HDMI1

HDMI2

HDMI3

HDMI4

HDMI

EQ/SW

DDC

CEC

TMDS

DDC

CEC

TMDS

DDC

CEC

TMDS

DDC

CEC

TMDS

HP Out

L/R

CVBS (TVOUT)

L/R (TVOUT)

YCbCr

L/R

L/R

SPDIF

RGB

CVBS

L/R

CVBS (SELOUT)

L/R (SELOUT)

RGB

CVBS/YC

RGB/HV

L/R

Audio

Amp

Side Video

YCbCr

L/R

S

E

L

/M

O

N

L

O

H

P

SPDIF

I2S 5.1ch

L/R

DAC

DDR2

1 Gb

IIC1

IIC2

NVM

Temp

Sensor

UART

II

C

II

C

II

C

Power SW

Key

IR

LED

PE-L

PE-L

TS

TS

LVDS(60/50Hz)

IIC_SINK

NICAM/A2

IIC0

II

C

Panel

120/100Hz

PE-L

Panel

60/50Hz FHD

Panel

60/50Hz WXGA

NAND

512Mbx2

TUS