12

DS8241-03 January 2014

www.richtek.com

RT8241

©

Copyright 2014 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.

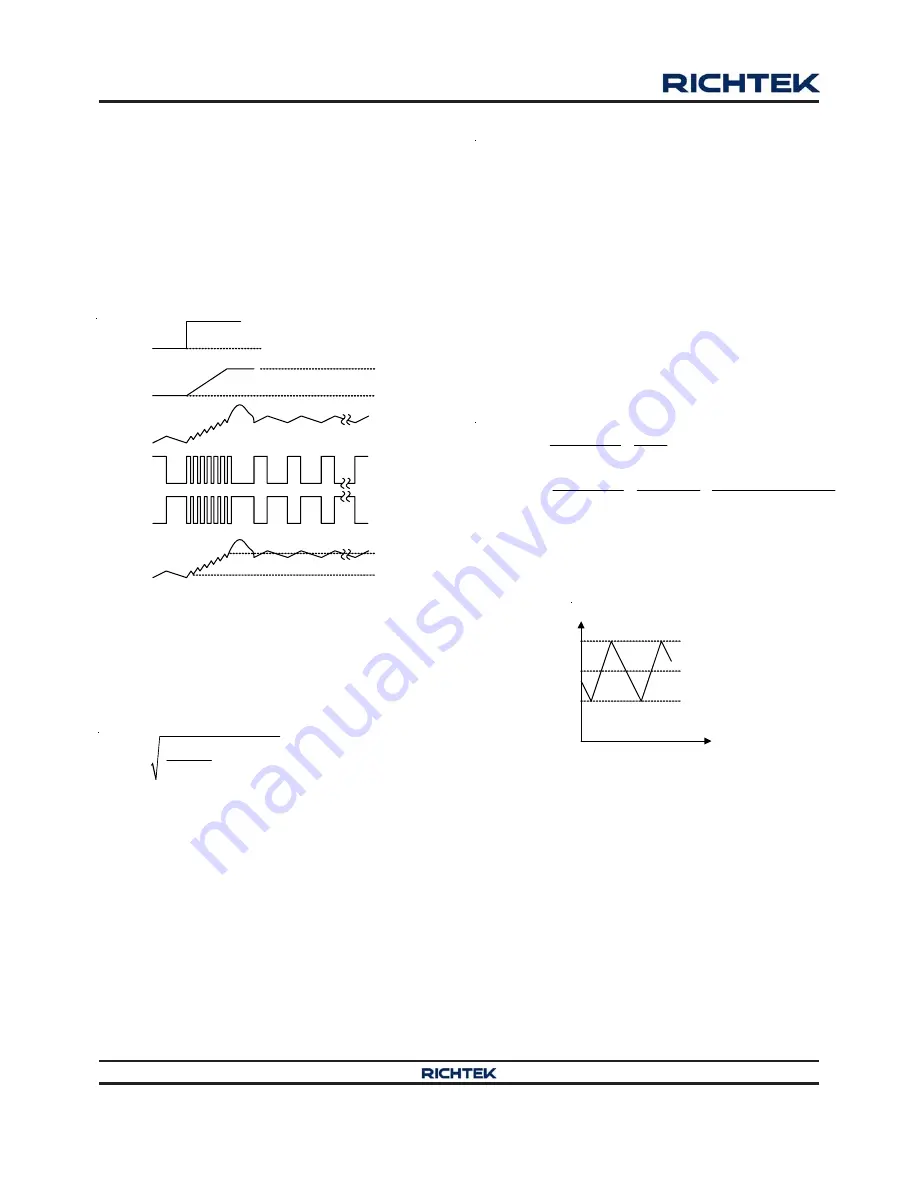

If the V

OUT

change is significant, there can be several

consecutive cycle of UGATE on-time followed by minimum

LGATE time. This can cause a rapid increase in inductor

current: typically it only takes a few switching cycles for

inductor current to rise up to the current limit. At some

point the V

FB

will rise up to the new internal V

REF

and the

UGATE pulses will cease, but the inductor's LI

2

energy

must then flow into the output capacitor. This can create

a significant overshoot, as shown in Figure 5.

Figure 5. Output Voltage Up Transition with

Overshooting

This overshoot can be approximated by the following

equation, where I

CL

is the current limit, V

FINAL

is the

desired set point for the final voltage, L is in

μ

H and C

OUT

is in

μ

F.

2

2

CL

MAX

FINAL

OUT

I

L

V

(

) V

C

×

=

+

Current Limit Setting (OCP)

The RT8241 has a cycle-by-cycle current limiting control.

The current limit circuit employs a unique

“

valley

”

current

sensing algorithm. If the magnitude of the current sense

signal at the CS pin is above the current limit threshold,

the PWM is not allowed to initiate a new cycle (Figure.

6). In order to provide both good accuracy and a cost

effective solution, the RT8241 supports temperature

compensated MOSFET R

DS(ON)

sensing. The CS pin

should be connected to GND through the trip voltage setting

resistor, R

CS

. The 10

μ

A CS terminal source current , I

CS

,

and the trip voltage setting resistor, R

CS

, set the CS trip

CS

CS

V

(mV) = R

(k ) 10( A)

μ

Ω ×

The Inductor current can be monitored by the voltage

between GND and the PHASE pin. Hence, the PHASE

pin should be connected to the drain terminal of the low

side MOSFET. I

CS

has temperature coefficient to

compensate the temperature dependency of the R

DS(ON)

.

GND is used as the positive current sensing node, so

GND should be connected to the source terminal of the

bottom MOSFET.

While the comparison is being done during the OFF state,

V

CS

sets the valley level of the inductor current. Thus, the

load current at over-current threshold, I

LOAD_OC

, can be

calculated as follows :

ripple

CS

LOAD_OC

DS(ON)

CS

IN

OUT

OUT

DS(ON)

SW

IN

I

V

I

8 R

2

V

(V

V

) V

1

8 R

2 L f

V

=

+

×

−

×

=

+

×

×

× ×

In an over-current condition, the current to the load exceeds

the current to the output capacitor, thus causing the output

voltage to fall. Eventually the voltage crosses the under

voltage protection threshold and the device shuts down.

Figure 6. “ Vally” Current Limit

Negative Over Current Limit (PWM Only Mode)

The RT8241 supports cycle-by-cycle negative over current

limiting in CCM Mode only. The over current limit is set to

be negative but is the same absolute value as the positive

over current limit. If output voltage continues to rise, the

low side MOSEFT remains on. Thus, the inductor current

is reduced and reverses direction after it reaches zero.

When there is too much negative current in the inductor,

the low side MOSFET is turned off and the current flows

towards V

IN

through the body diode of the high side

MOSFET. Because this protection limits the discharge

current of the output capacitor, the output voltage tends

0

I

L

t

I

L_Peak

I

LOAD

I

LIM

voltage, V

CS

, as in the following equation.

GND

Gx

V

REF

Initial V

REF

Final V

REF

V

FB

UGATE

LGATE

Initial V

OUT

Final V

OUT

V

OUT